# Élan<sup>™</sup>SC400 and ÉlanSC410 Microcontrollers User's Manual

| © 1997 Advanced Micro Devices, Inc. All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Micro Devices, Inc. ("AMD") reserves the right to make changes in its products without notice in order to improve design or performance characteristics.                                                                                                                                                                                                                                                                                                                                                                                             |

| The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication.                                                                                                 |

| This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied warranty of merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or systems without AMD's written approval. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products except as provided in AMD's Terms and Conditions of Sale for such products. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Trademarks  AMD, the AMD logo and combinations thereof are trademarks of Advanced Micro Devices, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Am386 and Am486 are registered trademarks, and Am186, Am188, E86, K86, Élan, Systems in Silicon, and AMD Facts-On-Demand are trademarks of Advanced Micro Devices, Inc. FusionE86 is a service mark of Advanced Micro Devices, Inc.  Microsoft and Windows are registered trademarks of Microsoft Corp.                                                                                                                                                                                                                                                       |

| Product names used in this publication are for identification purposes and may be trademarks of their respective companies.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## IF YOU HAVE QUESTIONS, WE'RE HERE TO HELP YOU.

### **Customer Service**

The AMD customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from the worldwide staff of AMD field application engineers and factory support staff to answer E86<sup>TM</sup> family hardware and software development questions.

## **Hotline and World Wide Web Support**

For answers to technical questions, AMD provides a toll-free number for direct access to our corporate applications hotline. Also available is the AMD World Wide Web home page and FTP site, which provides the latest E86 family product information, including technical information and data on upcoming product releases.

For technical support questions on all E86 products, send E-mail to lpd.support@amd.com.

## **Corporate Applications Hotline**

Additional contact information is listed on the back of this manual.

toll-free for U.S. and Canada (800) 222-9323

44-(0) 1276-803-299 U.K. and Europe hotline

## **World Wide Web Home Page and FTP Site**

To access the AMD home page go to http://www.amd.com.

To download documents and software, ftp to ftp.amd.com and log on as anonymous using your E-mail address as a password. Or via your web browser, go to ftp://ftp.amd.com.

Questions, requests, and input concerning AMD's WWW pages can be sent via E-mail to webmaster@amd.com.

#### **Documentation and Literature**

Free E86 family information such as data books, user's manuals, data sheets, application notes, the FusionE86<sup>SM</sup> Partner Solutions Catalog, and other literature is available with a simple phone call. Internationally, contact your local AMD sales office for complete E86 family literature.

#### Literature Ordering

(000) 222 0222

| (800) 222-9323 | toll-free for U.S. and Canada                                      |

|----------------|--------------------------------------------------------------------|

| (512) 602-5651 | direct dial worldwide                                              |

| (512) 602-7639 | fax                                                                |

| (800) 222-9323 | AMD Facts-On-Demand™ faxback service toll-free for U.S. and Canada |

iii

## **TABLE OF CONTENTS**

| PREFACE    | INTRODUCTION                                                                                       |     |

|------------|----------------------------------------------------------------------------------------------------|-----|

|            | ÉlanSC400 and ÉlanSC410 Microcontrollersx                                                          | CΧİ |

|            | Purpose of This Manual                                                                             | (Xi |

|            | Intended Audiencex                                                                                 | (Xi |

|            | Overview of This Manualx                                                                           | (Xi |

|            | Related Documents                                                                                  | ίv  |

|            | AMD Documentationxx                                                                                | ίv  |

|            | Additional Information                                                                             | ίv  |

|            | Documentation Conventions                                                                          | X۷  |

| CHAPTER 1  | ARCHITECTURAL OVERVIEW 1-                                                                          | -1  |

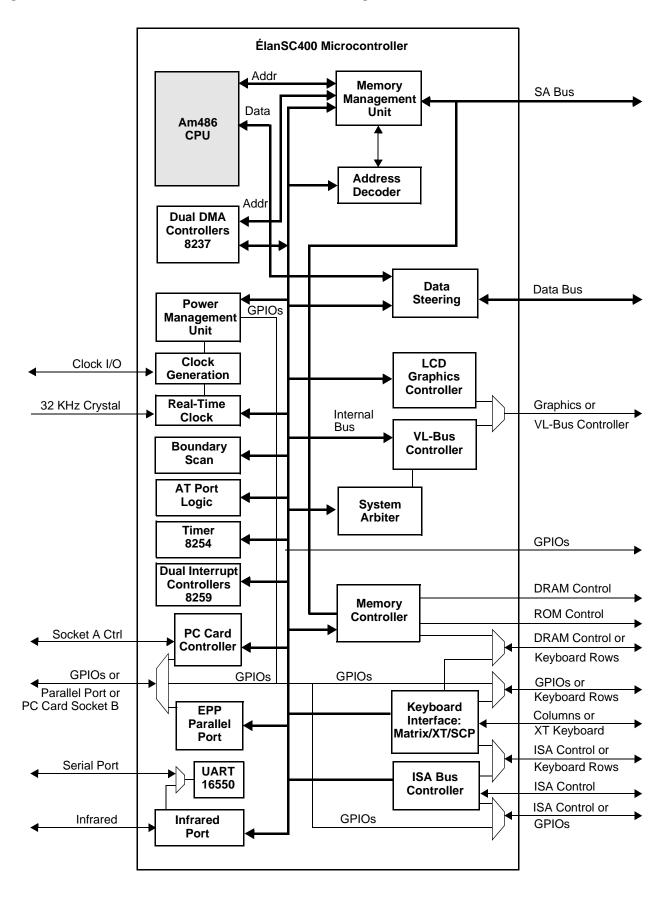

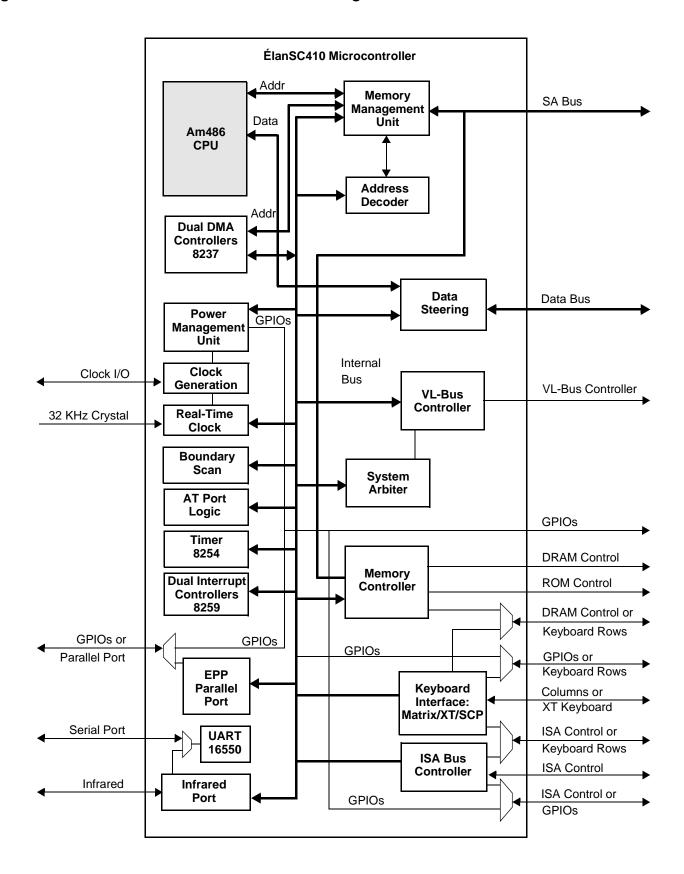

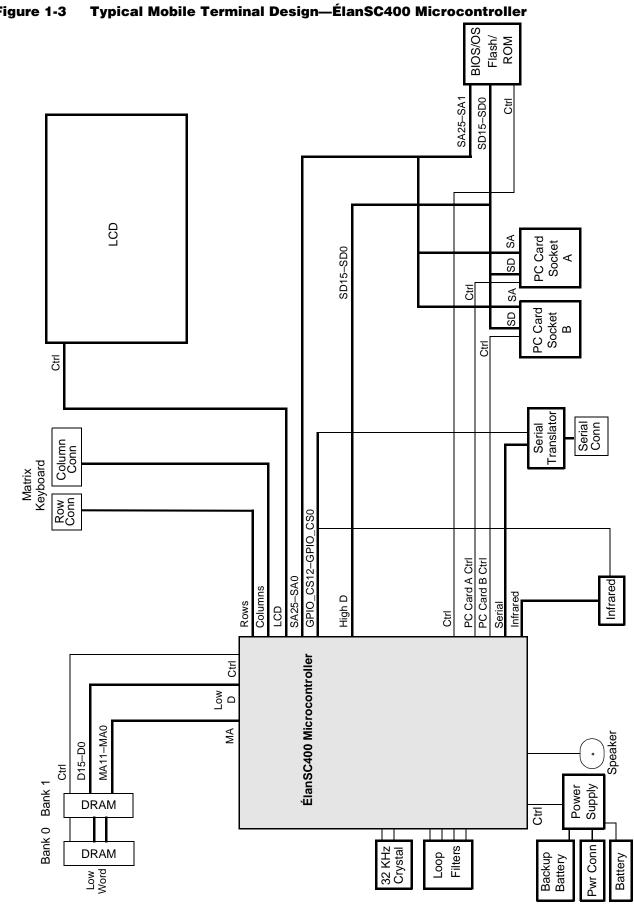

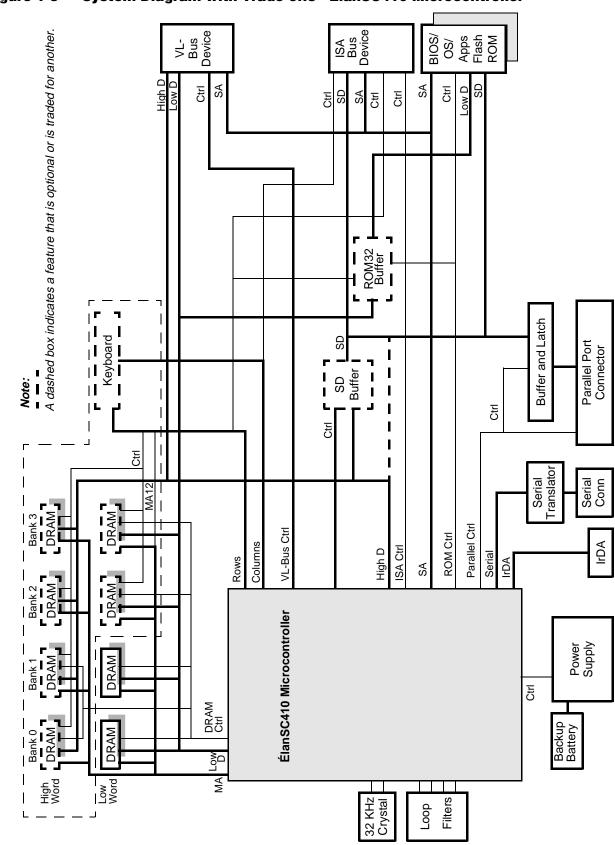

| OHAI IER I | 1.1 ÉlanSC400 and ÉlanSC410 Microcontrollers1                                                      |     |

|            | 1.1.1 ÉlanSC400 Microcontroller                                                                    |     |

|            | 1.1.2 ÉlanSC410 Microcontroller                                                                    |     |

|            | 1.2 Architectural Overview                                                                         |     |

|            | 1.2.1 Low-Voltage Am486 CPU Core1-                                                                 |     |

|            | 1.2.2 Power Management                                                                             |     |

|            | 1.2.3 Clock Generation                                                                             |     |

|            | 1.2.4 ROM/Flash Interface                                                                          |     |

|            | 1.2.5 DRAM Controller                                                                              |     |

|            | 1.2.6 Integrated Standard PC/AT Peripherals                                                        |     |

|            | 1.2.6.1 Dual DMA Controllers                                                                       |     |

|            | 1.2.6.2 Dual Interrupt Controllers                                                                 |     |

|            | 1.2.6.3 Programmable Interval Timer (PIT)                                                          |     |

|            | 1.2.6.4 Real-Time Clock (RTC)                                                                      | _O  |

|            | 1.2.6.5 PC/AT Support Features                                                                     |     |

|            | 1.2.7 Bidirectional Enhanced Parallel Port (EPP)                                                   |     |

|            | 1.2.8 Serial Port                                                                                  |     |

|            | 1.2.9 Keyboard Interfaces                                                                          |     |

|            | 1.2.10 Programmable General-Purpose Inputs and Outputs                                             |     |

|            | 1.2.11 Infrared Port1-1                                                                            |     |

|            | 1.2.12 Dual PC Card Controller (ÉlanSC400 Microcontroller Only) 1-1                                |     |

|            | 1.2.13 Graphics Controller (ÉlanSC400 Microcontroller Only) 1-1                                    |     |

|            | 1.2.14 JTAG Test Features                                                                          |     |

|            | 1.2.15 System Interfaces                                                                           |     |

|            | 1.2.15.1 Data Buses                                                                                |     |

|            |                                                                                                    |     |

|            | 1.2.15.2 Address Buses                                                                             |     |

|            | 1.2.15.3 Memory Management                                                                         |     |

|            | 1.2.15.4 ISA Bus Interface For External ISA Peripherals 1-1 1.2.15.5 VESA Local (VL) Bus Interface |     |

|            | 1.2.15.5 VESA Local (VL) Bus interface                                                             |     |

|            | LO OVAIGII COHAIDEIAHOHA                                                                           | . r |

| <b>CHAPTER 2</b> | <b>CONFIGURAT</b>      | ION BASICS                                                                                                    | 2-1                |

|------------------|------------------------|---------------------------------------------------------------------------------------------------------------|--------------------|

|                  | 2.1 Overview           |                                                                                                               | 2-1                |

|                  | 2.2 Configura          | tion Methods                                                                                                  | 2-1                |

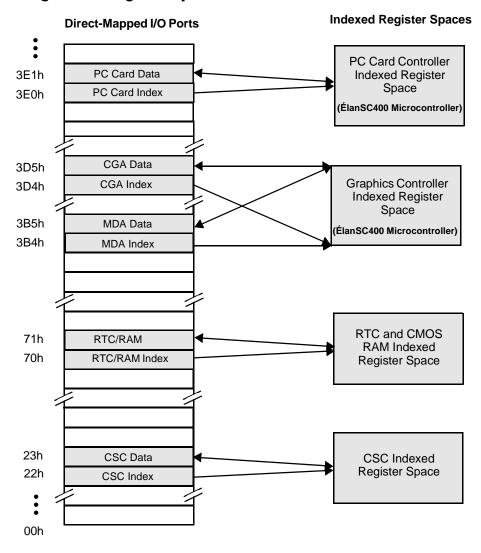

|                  | 2.3 Configura          | tion Register Spaces And Indexed Addressing                                                                   | 2-2                |

|                  |                        | rect-Mapped Registers                                                                                         |                    |

|                  |                        | direct-Mapped Registers (Indexed Registers)                                                                   |                    |

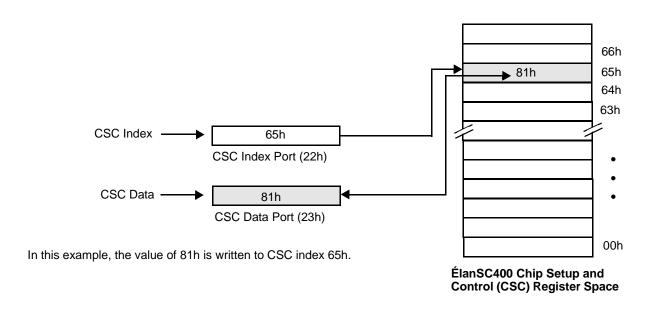

|                  |                        | nip Setup and Control (CSC) Indexed Registers                                                                 |                    |

|                  |                        | rade-Offs                                                                                                     |                    |

|                  |                        | n Multiplexing                                                                                                |                    |

|                  |                        | n Termination                                                                                                 |                    |

|                  |                        |                                                                                                               |                    |

| CHAPTER 3        | Am486 <sup>®</sup> CPU |                                                                                                               | 3-1                |

|                  |                        |                                                                                                               |                    |

|                  |                        |                                                                                                               | 3-1                |

|                  | 3.3 CPU featu          | res Specific to the ÉlanSC400 and ÉlanSC410                                                                   |                    |

|                  |                        | rollers                                                                                                       |                    |

|                  |                        | mory Management                                                                                               |                    |

|                  |                        | anagement Mode (SMM)                                                                                          |                    |

|                  | 3.5.1 U                | ses of SMM                                                                                                    | 3-3                |

|                  |                        | MM Requirements                                                                                               |                    |

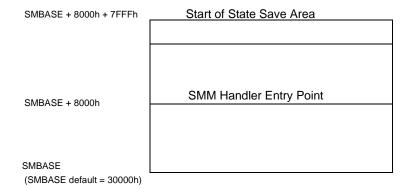

|                  | 3.5.3 S                | stem Management Random Access Memory (SMRAM)                                                                  | 3-4                |

|                  | 3.5.4 S                | stem Management Interrupt (SMI)                                                                               | 3-5                |

|                  | 3.                     | 5.4.1 State Save Map                                                                                          | 3-6                |

|                  | 3.5.5 S                | MM Execution Environment                                                                                      | 3-8                |

|                  | 3.5.6 E                | cceptions and Interrupts                                                                                      | 3-9                |

|                  | 3.5.7 A                | uto Halt Restart                                                                                              | . 3-10             |

|                  |                        | O Trapping                                                                                                    |                    |

|                  |                        | 5.8.1 Restarting I/O Instructions                                                                             |                    |

|                  |                        | 5.8.2 Emulating I/O Instructions                                                                              |                    |

|                  |                        | MM Base Relocation Example                                                                                    |                    |

|                  |                        | MM Interaction With SRESET                                                                                    |                    |

|                  |                        | Identification Using the CPUID Instruction                                                                    |                    |

|                  |                        | PUID Timing                                                                                                   |                    |

|                  |                        |                                                                                                               |                    |

|                  |                        | PUID Operation                                                                                                |                    |

|                  |                        | PUID Example                                                                                                  |                    |

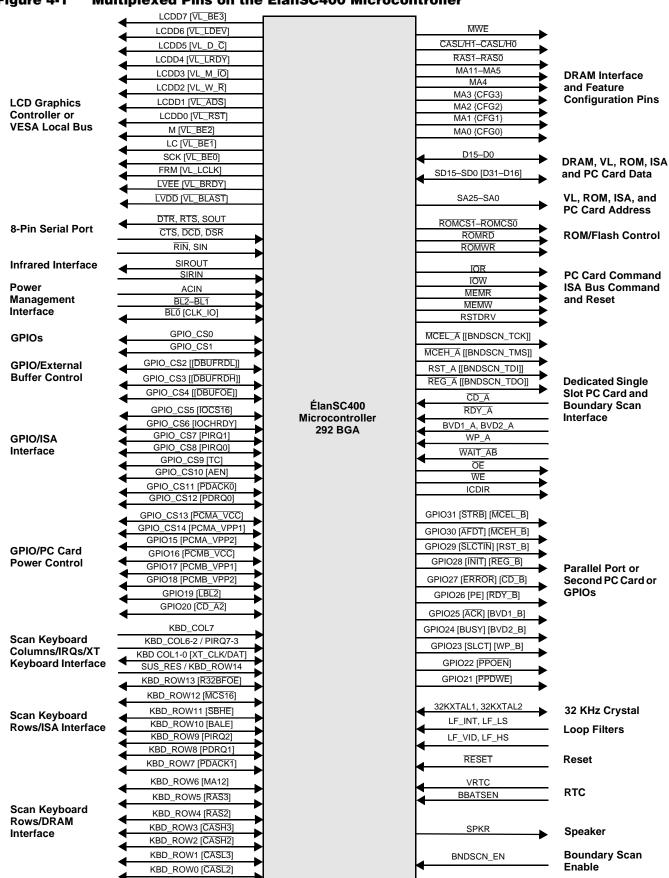

| CHAPTER 4        | SYSTEM INTE            |                                                                                                               | 4-1                |

|                  |                        | on                                                                                                            |                    |

|                  | •                      | pes of Reset                                                                                                  |                    |

|                  |                        | 1.1.1 Power-On Reset                                                                                          |                    |

|                  |                        | 1.1.2 Am486 CPU DX Register at CPU Reset                                                                      |                    |

|                  |                        | scriptions.                                                                                                   |                    |

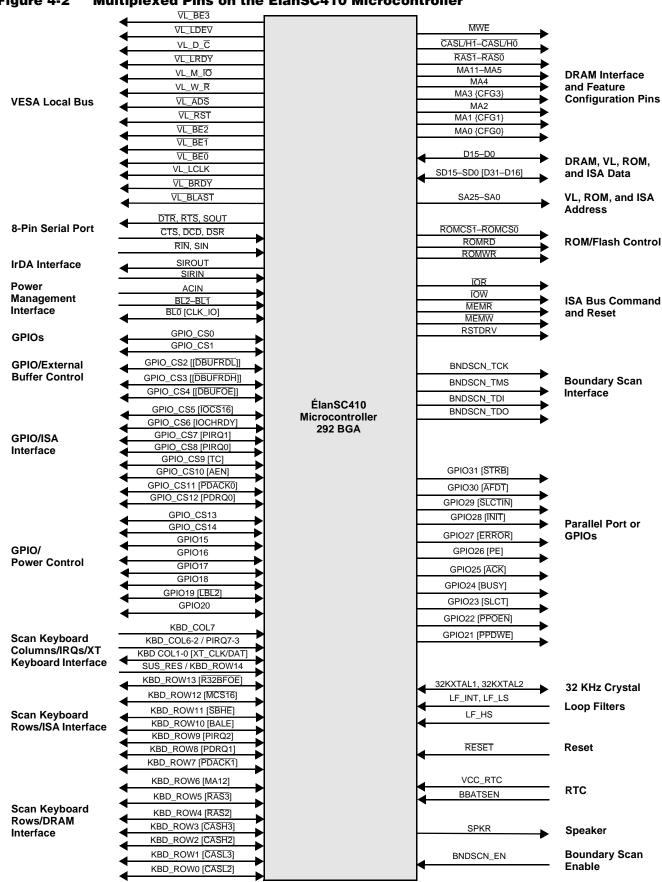

|                  | 4.3 Pin Chang          | es for the ÉlanSC410 Microcontroller                                                                          | . 4-13             |

|                  |                        | d Pin Function Options                                                                                        |                    |

|                  | 4.4.1 U                | sing the Configuration Pins to Select Pin Functions                                                           | . 4-16             |

|                  | 4.                     | 4.1.1 CFG0 and CFG1 Pins                                                                                      | . 4-16             |

|                  | 4.                     | 4.1.2 CFG2 Pin                                                                                                | . 4-17             |

|                  | 4.                     | 4.1.3 CFG3 Pin                                                                                                | . 4-17             |

|                  |                        | 4.1.4 BNDSCN_EN Pin                                                                                           |                    |

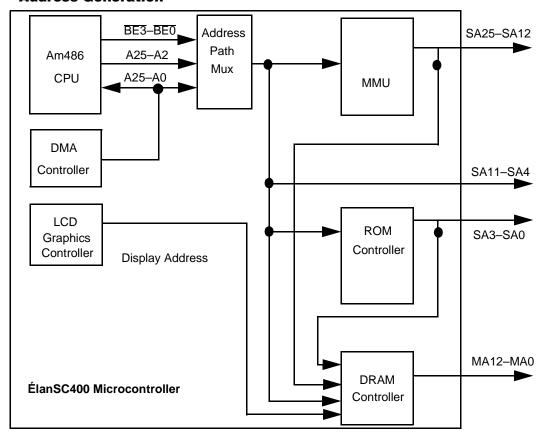

|                  |                        | Address Buses                                                                                                 |                    |

|                  |                        | ata Buses                                                                                                     |                    |

|                  |                        | 5.1.1 Configuration A: 16-Bit DRAM Bus and 16-Bit SD Bus                                                      |                    |

|                  |                        | 5.1.2 Configuration B: 32-Bit DRAM Bus and 16-Bit SD Bus                                                      |                    |

|                  |                        | 5.1.2 Configuration B. 32-Bit DRAM Bus, 16-Bit SD Bus, 5.1.3 Configuration C: 32-Bit DRAM Bus, 16-Bit SD Bus, | . <del>-</del> -13 |

|                  | 4.                     | and 32-Bit ROM Bus                                                                                            | <b>1</b> -10       |

|                  | 4                      | 5 1 4 Data Daths                                                                                              |                    |

|               |     | 4.5.2   | Address Buses                                                                     |                                      |

|---------------|-----|---------|-----------------------------------------------------------------------------------|--------------------------------------|

|               | 4.6 | System  | Interfaces                                                                        | . 4-25                               |

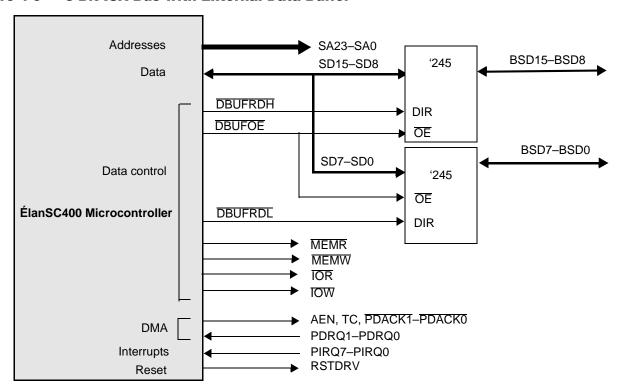

|               | 4.7 | ISA Bus | s Interface                                                                       | . 4-25                               |

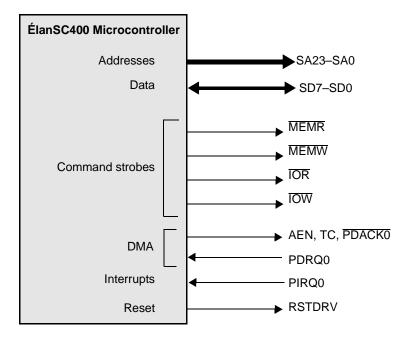

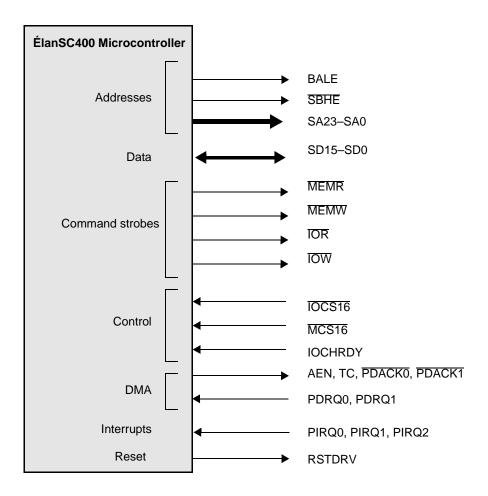

|               |     | 4.7.1   | Overview                                                                          | . 4-25                               |

|               |     | 4.7.2   | Registers                                                                         |                                      |

|               |     | 4.7.3   | Block Diagram                                                                     |                                      |

|               |     | 4.7.4   | Supported ISA Signals                                                             |                                      |

|               |     | 4.7.5   | Operation                                                                         |                                      |

|               |     | 4.7.5   | 4.7.5.1 Bus Speeds                                                                |                                      |

|               |     |         | 4.7.5.1 Bus speeds                                                                |                                      |

|               |     |         |                                                                                   |                                      |

|               |     |         | 4.7.5.3 Command Strobes                                                           |                                      |

|               |     | 4 7 0   | 4.7.5.4 External Buffer Control Signals                                           |                                      |

|               |     | 4.7.6   | Using the ISA Bus for Debugging                                                   |                                      |

|               |     |         | 4.7.6.1 Echoing Direct-Mapped PC/AT Registers                                     |                                      |

|               |     |         | 4.7.6.2 Echoing CSC Indexed Registers                                             |                                      |

|               |     | 4.7.7   | Initialization                                                                    |                                      |

|               |     | 4.7.8   | Power Management                                                                  |                                      |

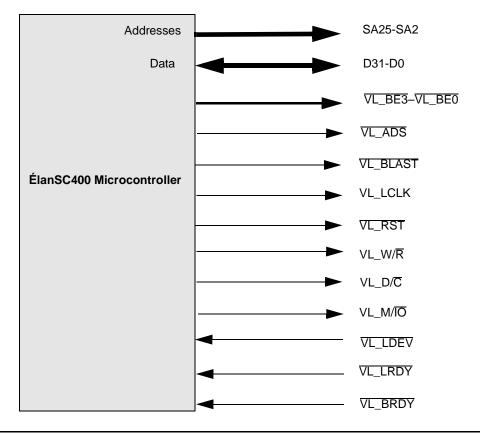

|               | 4.8 | VESA L  | ocal (VL) Bus Controller                                                          | . 4-35                               |

|               |     | 4.8.1   | Overview                                                                          | . 4-35                               |

|               |     | 4.8.2   | Registers                                                                         | . 4-35                               |

|               |     | 4.8.3   | Block Diagram                                                                     | . 4-36                               |

|               |     | 4.8.4   | Operation                                                                         |                                      |

|               |     |         | 4.8.4.1 Address Interface                                                         |                                      |

|               |     |         | 4.8.4.2 Data Interface                                                            |                                      |

|               |     |         | 4.8.4.3 Normal Bus Cycles                                                         |                                      |

|               |     |         | 4.8.4.4 Special Bus Cycles                                                        |                                      |

|               |     |         | 4.8.4.5 Unsupported VL-Bus Signal                                                 |                                      |

|               |     | 4.8.5   | Initialization                                                                    |                                      |

|               |     | 4.8.6   | Power Management                                                                  |                                      |

|               | 4.0 |         |                                                                                   |                                      |

|               | 4.9 |         | Port Logic                                                                        |                                      |

|               |     | 4.9.1   | Overview                                                                          |                                      |

|               |     | 4.9.2   | Registers                                                                         |                                      |

|               |     |         | 4.9.2.1 Direct-Mapped Registers                                                   | . 4-39                               |

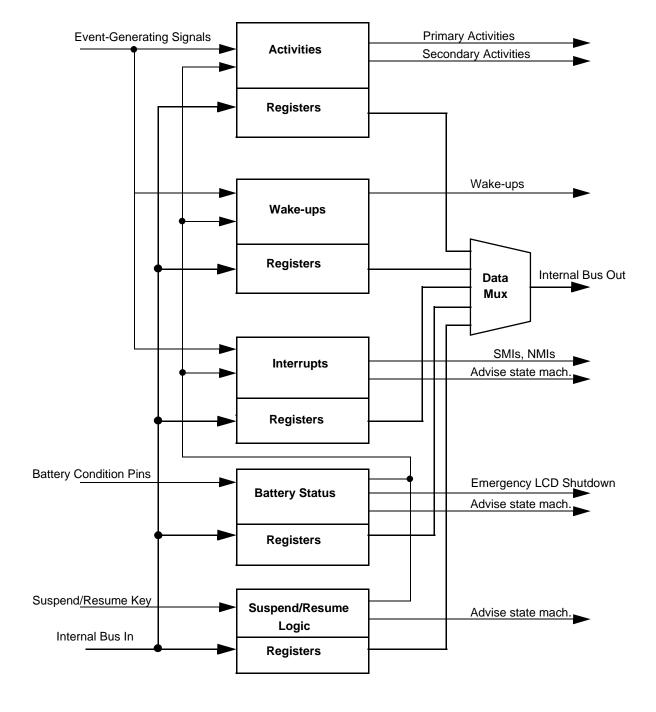

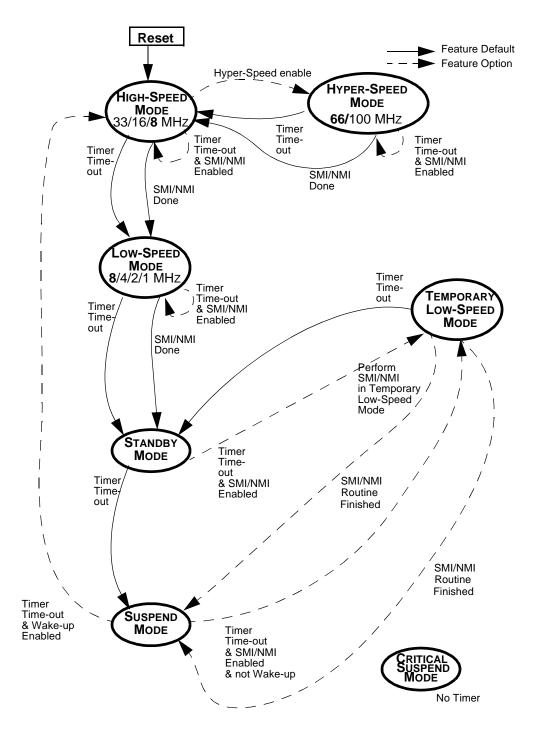

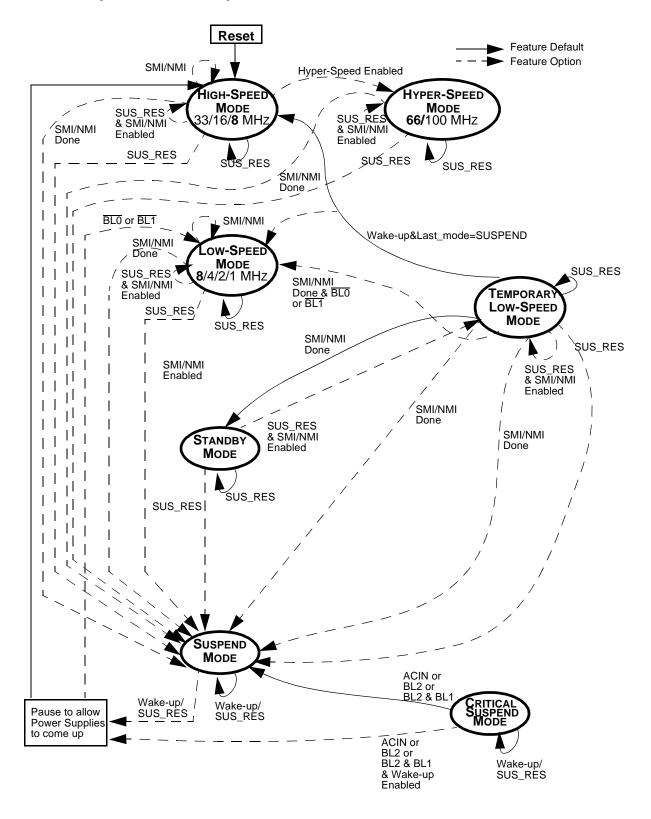

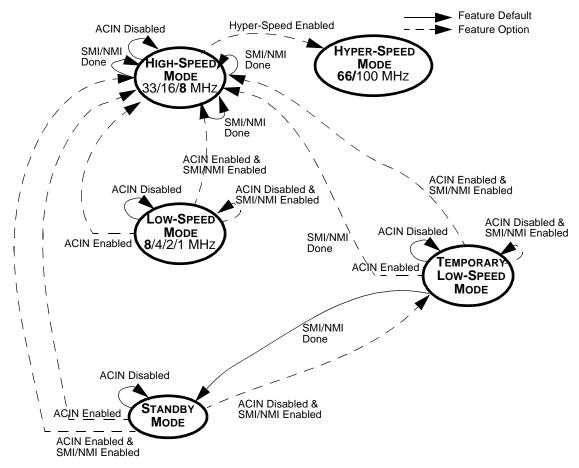

| CHAPTER 5     | PΟ\ | WER MA  | NAGEMENT                                                                          | 5-1                                  |

| 011711 1211 0 | _   |         | W                                                                                 | _                                    |

|               | 0   | 5.1.1   | PMU Terms                                                                         |                                      |

|               | 5.2 |         | rs                                                                                |                                      |

|               | J.Z | 5.2.1   | PMU Mode Control and Status Registers                                             | 5-2                                  |

|               | E 2 |         |                                                                                   |                                      |

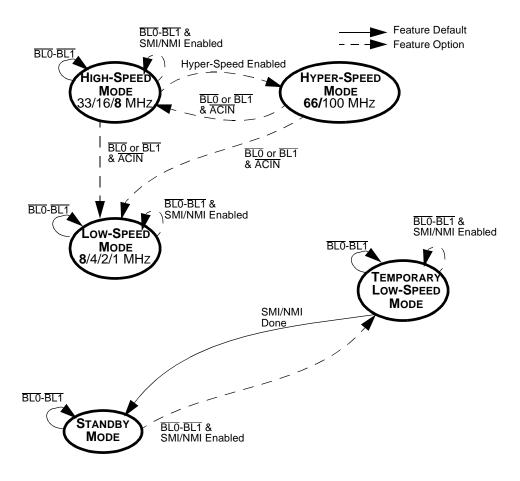

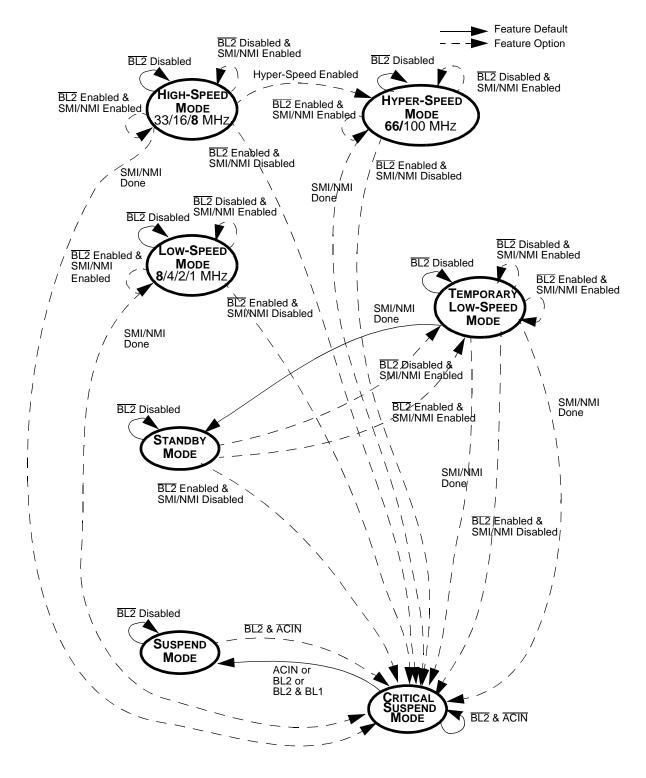

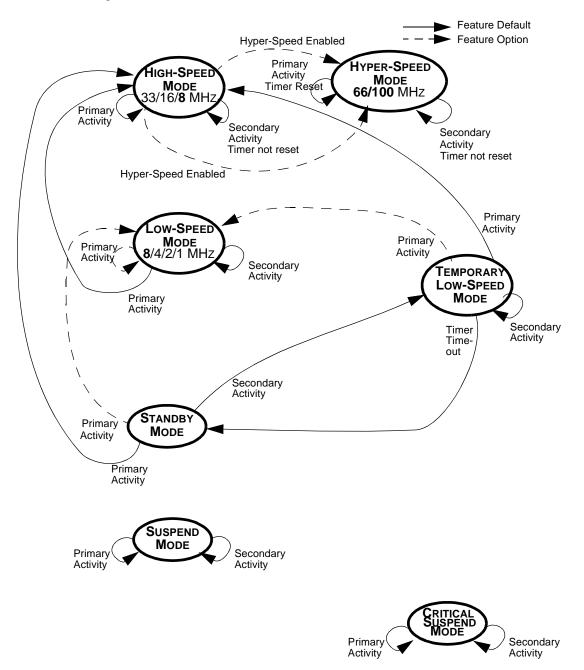

|               |     |         | liagram                                                                           |                                      |

|               | 5.4 | •       | on                                                                                |                                      |

|               |     | 5.4.1   | Hyper-Speed Mode                                                                  |                                      |

|               |     |         | 5.4.1.1 Actions Taken During Hyper-Speed Mode                                     |                                      |

|               |     |         | 5.4.1.2 Entering Hyper-Speed Mode                                                 |                                      |

|               |     |         | 5.4.1.3 Leaving Hyper-Speed Mode                                                  |                                      |

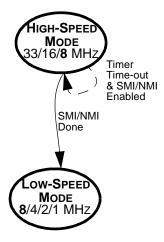

|               |     | 5.4.2   | High-Speed Mode                                                                   |                                      |

|               |     |         | 5.4.2.1 Actions Taken During High-Speed Mode                                      |                                      |

|               |     |         | 5.4.2.2 Entering High-Speed Mode                                                  |                                      |

|               |     |         | 5.4.2.3 Leaving High-Speed Mode                                                   |                                      |

|               |     | 5.4.3   | Low-Speed Mode                                                                    |                                      |

|               |     |         | 5.4.3.1 Actions Taken During Low-Speed Mode                                       | . 5-13                               |

|               |     |         |                                                                                   |                                      |

|               |     |         | 5.4.3.2 Entering Low-Speed Mode                                                   | . 5-13                               |

|               |     |         | <ul><li>5.4.3.2 Entering Low-Speed Mode</li></ul>                                 |                                      |

|               |     | 5.4.4   | 5.4.3.3 Leaving Low-Speed mode                                                    | . 5-13                               |

|               |     | 5.4.4   | 5.4.3.3 Leaving Low-Speed mode                                                    | . 5-13<br>. 5-14                     |

|               |     | 5.4.4   | 5.4.3.3Leaving Low-Speed modeStandby Mode5.4.4.1Actions Taken During Standby Mode | . 5-13<br>. 5-14<br>. 5-14           |

|               |     | 5.4.4   | 5.4.3.3 Leaving Low-Speed mode                                                    | . 5-13<br>. 5-14<br>. 5-14<br>. 5-14 |

|           |     | 5.4.5     | Suspend    | d Mode                                        | 5-15 |

|-----------|-----|-----------|------------|-----------------------------------------------|------|

|           |     |           | 5.4.5.1    | Actions Taken During Suspend Mode             | 5-15 |

|           |     |           | 5.4.5.2    | Entering Suspend Mode                         | 5-15 |

|           |     |           | 5.4.5.3    | Leaving Suspend Mode                          | 5-15 |

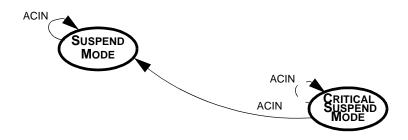

|           |     | 5.4.6     | Critical S | Suspend Mode                                  | 5-16 |

|           |     |           | 5.4.6.1    | Actions Taken During Critical Suspend Mode    | 5-16 |

|           |     |           | 5.4.6.2    | Entering Critical Suspend Mode                | 5-16 |

|           |     |           | 5.4.6.3    | Leaving Critical Suspend Mode                 | 5-16 |

|           |     | 5.4.7     | Tempora    | ary Low-Speed Mode                            | 5-17 |

|           |     |           |            | Actions Taken During Temporary Low-Speed Mode |      |

|           |     |           |            | Entering Temporary Low-Speed Mode             |      |

|           |     |           |            | Leaving Temporary Low-Speed Mode              |      |

|           |     | 5.4.8     |            | owcharts                                      |      |

|           |     | 5.4.9     |            | p Sources                                     |      |

|           |     | 5.4.10    |            | -Purpose I/O (GPIO) Pins                      |      |

|           |     |           |            | Mappable GPIO_PMUA-GPIO_PMUD Signals          |      |

|           |     | 5.4.11    |            | etect and Battery Low                         |      |

|           |     |           |            | ACIN                                          |      |

|           |     |           |            | Battery Low                                   |      |

|           |     | 5.4.12    |            | I Generation                                  |      |

|           |     |           |            | I/O Access SMIs                               |      |

|           |     | 5.4.13    | •          | Monitor                                       |      |

|           |     |           |            | Using the Activity Source Flag Registers      |      |

|           |     | 5.4.14    |            | otions in PMU Modes                           |      |

|           |     |           |            | Suspend State Options                         |      |

|           | 5.5 | Initializ |            | Programmable Pull-Up and Pull-Down Options    |      |

|           |     |           |            |                                               |      |

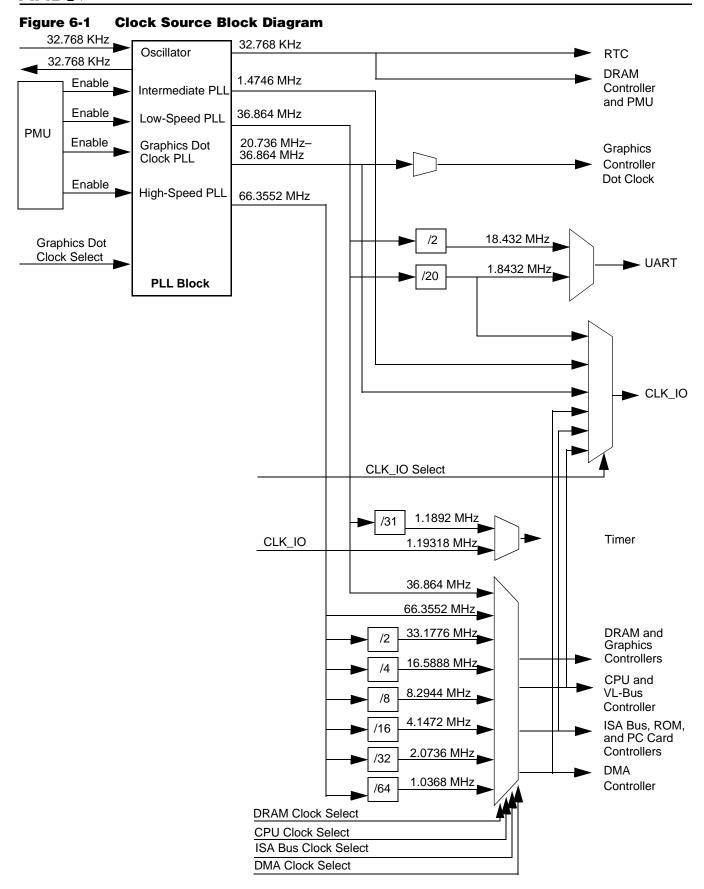

| CHAPTER 6 |     |           | NTROL      |                                               | 6-1  |

|           |     |           |            |                                               |      |

|           |     |           |            |                                               |      |

|           |     |           | _          |                                               |      |

|           | 6.4 | •         |            |                                               |      |

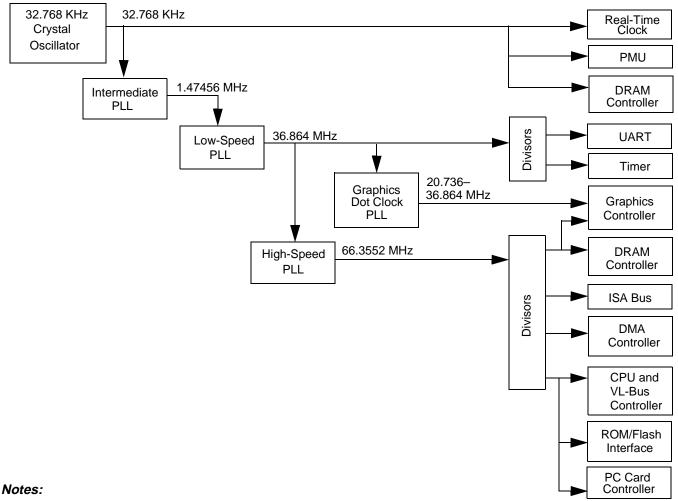

|           |     | 6.4.1     |            | eneration                                     |      |

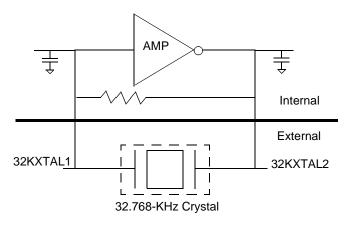

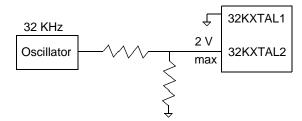

|           |     |           |            | 32-KHz Crystal Oscillator                     |      |

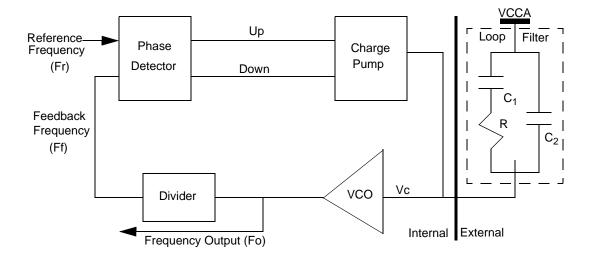

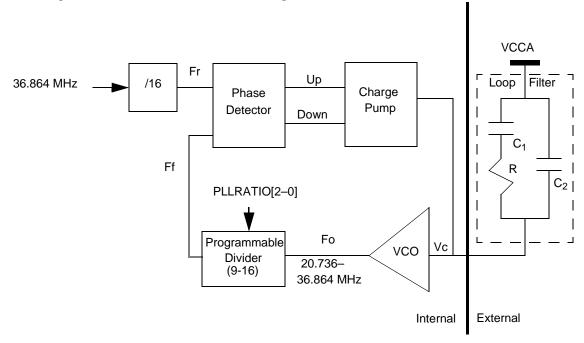

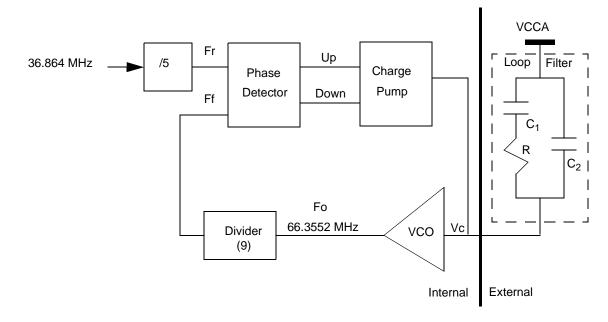

|           |     |           |            | Intermediate and Low-Speed PLLs               |      |

|           |     |           |            | High-Speed PLL                                |      |

|           |     | 6.4.2     |            | ontrol                                        |      |

|           |     | 0.4.2     | 6.4.2.1    | CPU 1x Clock                                  |      |

|           |     |           | 6.4.2.2    | Memory Clock                                  |      |

|           |     |           |            | Timer Clock                                   |      |

|           |     |           |            | UART Clock                                    |      |

|           |     |           |            | System Clock                                  |      |

|           |     |           |            | RTC Clock                                     |      |

|           |     |           |            | DMA Clock                                     |      |

|           | 6.5 | Initializ |            |                                               |      |

|           |     |           |            | nent                                          |      |

| CHAPTER 7 | MEMORY MANAGEMENT 7-1                                   |

|-----------|---------------------------------------------------------|

|           | 7.1 Overview                                            |

|           | 7.2 Registers                                           |

|           | 7.3 Address Decoding and Aliasing                       |

|           | 7.3.1 Internal Address Bus Size7-3                      |

|           | 7.3.2 Special Handling for A20                          |

|           | 7.3.3 Top of Memory CPU Execution                       |

|           | 7.3.4 ISA Bus Addressing7-4                             |

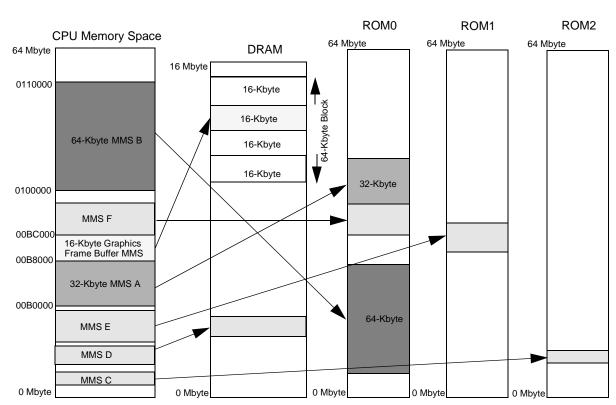

|           | 7.4 Multiple Memory Spaces                              |

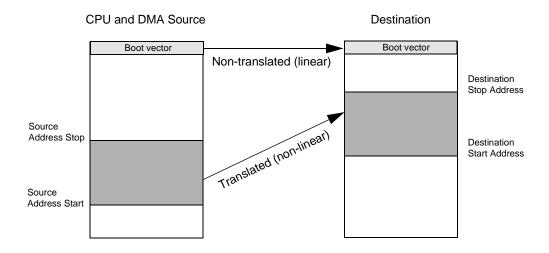

|           | 7.5 Non-Translated Memory Management7-6                 |

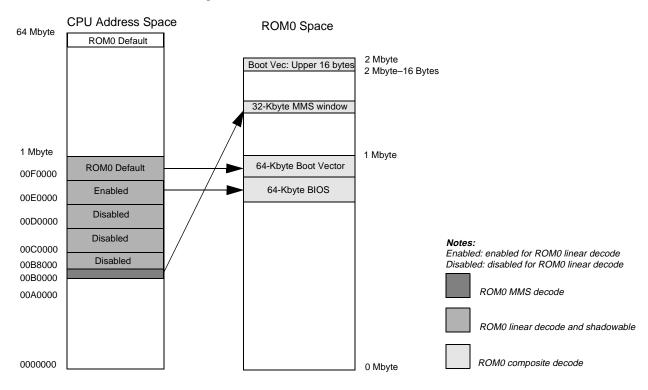

|           | 7.5.1 ROM0 and Non-Translated Memory Management7-6      |

|           | 7.5.2 DRAM and Non-Translated Memory Management7-7      |

|           | 7.6 Translated Memory Management                        |

|           | 7.6.1 MMS Windows A and B                               |

|           | 7.6.2 MMS Windows C, D, E, and F                        |

|           | 7.6.3 Graphics Frame Buffer MMS Window7-9               |

|           | 7.6.4 PC Card Memory Management7-10                     |

|           | 7.6.4.1 Standard 82365 PC Card Control                  |

|           | 7.6.4.2 Simplified PC Card Control                      |

|           | 7.7 System Considerations7-11                           |

|           | 7.7.1 <u>2.7-Volt Operation</u>                         |

|           | 7.7.2 ROMCS2 Operation                                  |

|           | 7.7.3 Memory Mapping and Caching                        |

|           | 7.7.3.1 Caching in System Management Mode               |

| CHAPTER 8 | ROM/FLASH INTERFACE 8-1                                 |

| 0         | 8.1 Overview                                            |

|           | 8.2 Registers                                           |

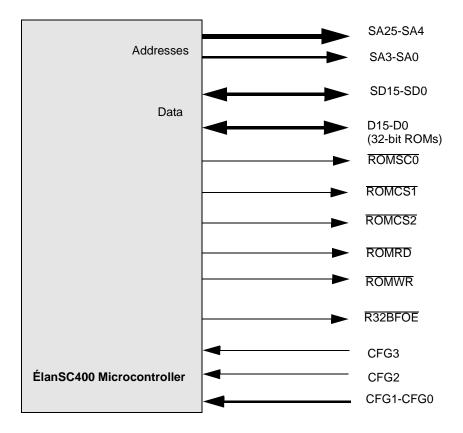

|           | 8.3 Block Diagram                                       |

|           | 8.4 Operation                                           |

|           | 8.4.1 Architectural Overview8-3                         |

|           | 8.4.2 Data Bus Usage                                    |

|           | 8.5 Initialization                                      |

|           | 8.5.1 Configuring the ROMCSO Interface Using Pin Straps |

|           | 8.5.2 Other ROMCSx Interface Configuration Options8-8   |

|           | 8.5.2.1 Data Width Control                              |

|           | 8.5.2.2 Access Speed                                    |

|           | 8.5.2.3 Early Chip Select                               |

|           | 8.6 Power Management                                    |

|           |                                                         |

| CHAPTER 9 | DRAM CONTROLLER 9-1                                     |

|           | 9.1 System Design                                       |

|           | 9.2 Registers                                           |

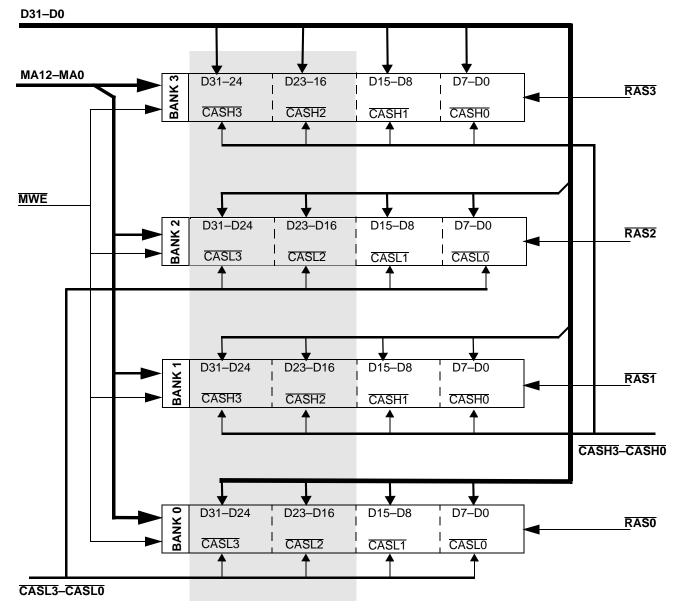

|           | 9.3 Block Diagram9-4                                    |

|           | 9.4 Operation                                           |

|           | 9.4.1 System Address Decoding                           |

|           | 9.4.1.1 RAS Strobe Assertion (Bank Selection)           |

|           | 9.4.1.2 CAS Strobe Assertion (Byte Lane Selection)      |

|           | 9.4.2 Timing and Control Signal Generation              |

|           | 9.4.2.1 Page Mode and RAS Time-Outs9-12                 |

|           | 9.4.2.2 MWE Generation                                  |

|           | 9.4.2.3 CAS Pulse Width9-12                             |

|           | 9.4.2.4 CAS Precharge Delay                             |

|           | 9.4.2.5 Refresh                                         |

|           | 9.5 Initialization                                      |

|           | 9.5.1 Boot Process Overview9-13                         |

|           | 9.5.2 Dynamic DRAM Detection Algorithm                  |

|           | 9.6 Power Management                                    |

| <b>CHAPTER 10</b> | DMA CONTROLLER                                        | 10-1   |

|-------------------|-------------------------------------------------------|--------|

|                   | 10.1 Overview                                         | . 10-1 |

|                   | 10.2 Registers                                        | . 10-1 |

|                   | 10.2.1 Direct-Mapped Registers                        | . 10-1 |

|                   | 10.2.2 Chip Configuration and Control (CSC) Registers | . 10-2 |

|                   | 10.2.2.1 Extended Page Registers                      | . 10-2 |

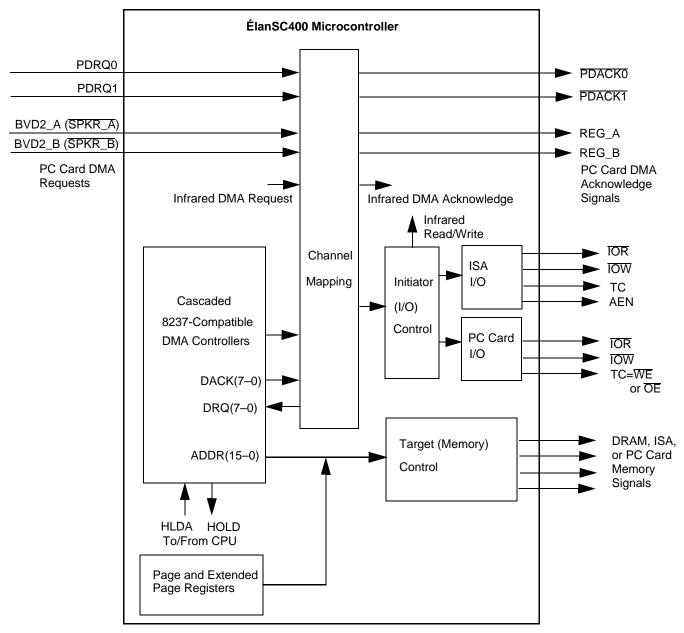

|                   | 10.3 Block Diagram                                    | . 10-3 |

|                   | 10.4 Operation                                        | . 10-5 |

|                   | 10.4.1 Addressing DMA Channels                        | . 10-5 |

|                   | 10.4.2 DMA Transfers                                  |        |

|                   | 10.4.2.1 Transfer Modes                               | . 10-7 |

|                   | 10.4.2.2 Autoinitialize                               | . 10-7 |

|                   | 10.4.2.3 Priority                                     |        |

|                   | 10.4.2.4 DMA Cycles                                   |        |

|                   | 10.4.3 DMA Channel Mapping                            |        |

|                   | 10.4.4 DMA Latency                                    |        |

|                   | 10.5 Initialization                                   |        |

|                   | 10.6 Power Management                                 | . 10-9 |

| <b>CHAPTER 11</b> | PROGRAMMABLE INTERRUPT CONTROLLER                     | 11-1   |

|                   | 11.1 Overview                                         | . 11-1 |

|                   | 11.2 Registers                                        | .11-1  |

|                   | 11.3 Block Diagram                                    | .11-2  |

|                   | 11.4 Operation                                        |        |

|                   | 11.4.1 IRQ Mapping                                    |        |

|                   | 11.4.2 Interrupt Vectors                              | . 11-5 |

|                   | 11.5 Initialization                                   | . 11-5 |

|                   | 11.6 Power Management                                 | . 11-6 |

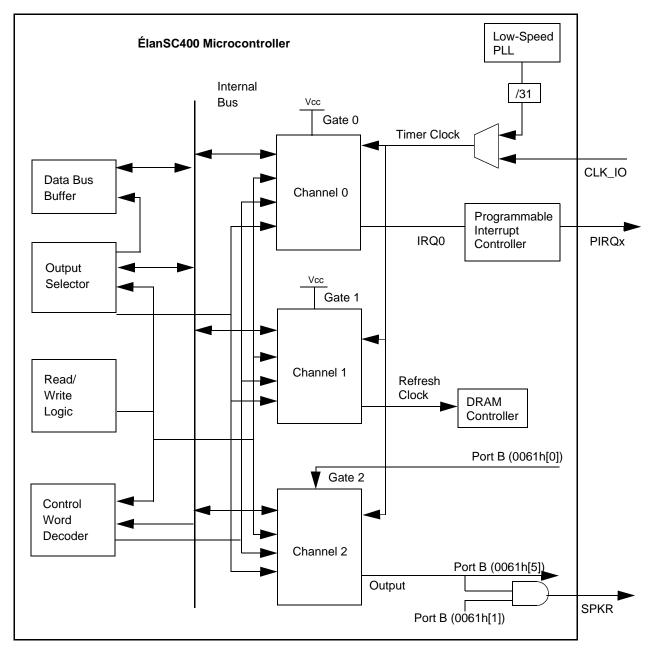

| <b>CHAPTER 12</b> | PROGRAMMABLE INTERVAL TIMER                           | 12-1   |

|                   | 12.1 Overview                                         | . 12-1 |

|                   | 12.2 Registers                                        |        |

|                   | 12.2.1 Direct-Mapped Registers                        |        |

|                   | 12.3 Block Diagram                                    |        |

|                   | 12.4 Operation                                        |        |

|                   | 12.4.1 Modes of Operation                             |        |

|                   | 12.4.1.1 Mode 0: Interrupt on Terminal Count          |        |

|                   | 12.4.1.2 Mode 1: Hardware-Retriggerable One-Shot      | . 12-3 |

|                   | 12.4.1.3 Mode 2: Rate Generator                       |        |

|                   | 12.4.1.4 Mode 3: Square Wave Mode                     |        |

|                   | 12.4.1.5 Mode 4: Software Triggered Strobe            |        |

|                   | 12.4.1.6 Mode 5: Hardware Triggered Strobe            |        |

|                   | 12.4.2 Timer Configuration                            |        |

|                   | 12.4.2.1 Configuring Timer Channel 0                  |        |

|                   | 12.4.2.2 Configuring Timer Channel 1                  |        |

|                   | 12.4.2.3 Configuring Timer Channel 2                  |        |

|                   | 12.4.3 Programming the Timer Channels                 |        |

|                   | 12.5 Initialization.                                  |        |

|                   | 12.6 Power Management                                 | . 12-6 |

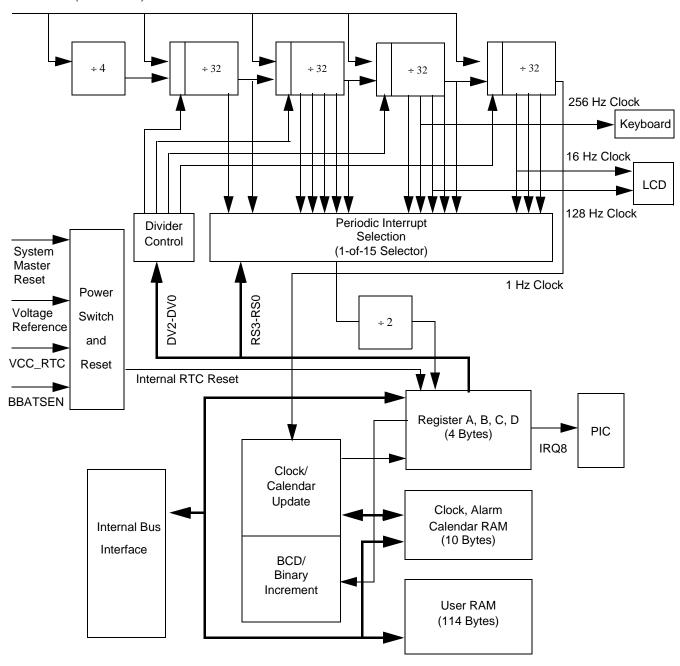

| <b>CHAPTER 13</b>                     | REAL-TIME CLOCK                                      | 13-1 |

|---------------------------------------|------------------------------------------------------|------|

|                                       | 13.1 Overview                                        |      |

|                                       | 13.2 Registers BAM Is dev Begisters                  |      |

|                                       | 13.2.1 RTC and Configuration RAM Index Registers     |      |

|                                       | 13.3 Block Diagram                                   |      |

|                                       | 13.4 Operation                                       |      |

|                                       | 13.4.1 Interrupts                                    |      |

|                                       | 13.4.2 RTC Clock                                     |      |

|                                       | 13.4.3 Internal Oscillator Control Bits              |      |

|                                       | 13.4.4 Update Cycle                                  |      |

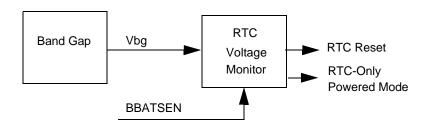

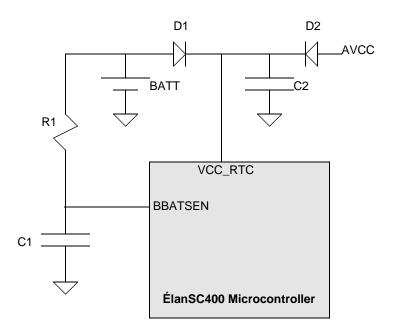

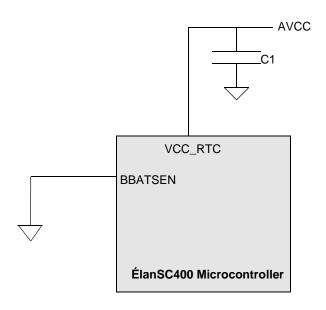

|                                       | 13.4.5 Backup Battery Considerations                 |      |

|                                       | 13.4.5.1 Using an External RTC Backup Battery        |      |

|                                       | 13.4.5.2 Not Using an External RTC Backup Battery    |      |

|                                       | 13.4.5.3 Overall System Implications                 |      |

|                                       | 13.5 Initialization                                  |      |

|                                       | 13.6 Power Management                                | 13-9 |

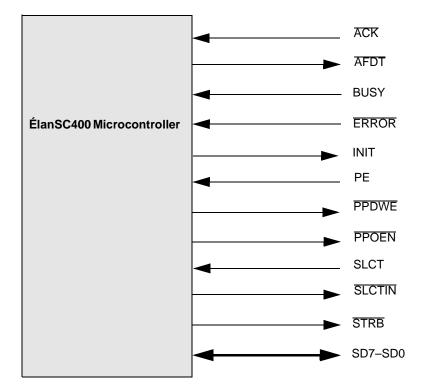

| CHAPTER 14                            | PARALLEL PORT                                        | 14-1 |

| · · · · · · · · · · · · · · · · · · · | 14.1 Overview                                        |      |

|                                       | 14.2 Registers                                       |      |

|                                       | 14.2.1 Direct-Mapped Registers                       |      |

|                                       | 14.2.2 Chip Setup and Control Registers              | 14-2 |

|                                       | 14.3 Block Diagram                                   |      |

|                                       | 14.4 Pin Definitions by Mode                         |      |

|                                       | 14.5 Operation                                       |      |

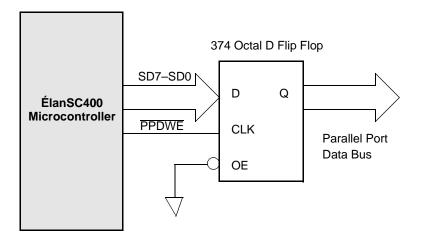

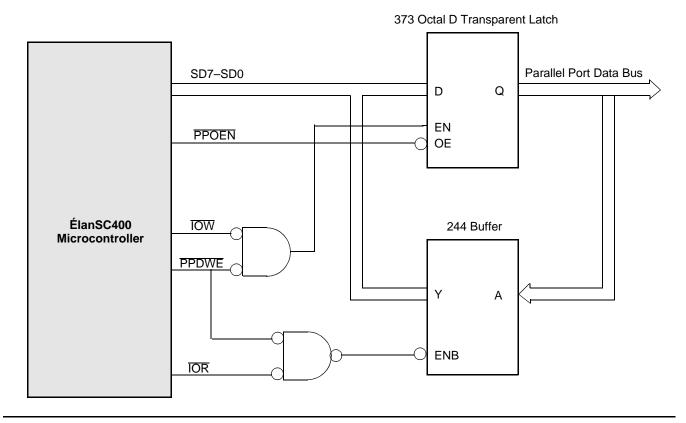

|                                       | 14.5.1 Minimal System Design                         |      |

|                                       | 14.5.1.1 PC/AT Compatible Mode                       |      |

|                                       | 14.5.1.2 Bidirectional and EPP Modes                 |      |

|                                       | 14.5.2 Operating Modes                               |      |

|                                       | 14.5.2.1 PC/AT Compatible Mode                       |      |

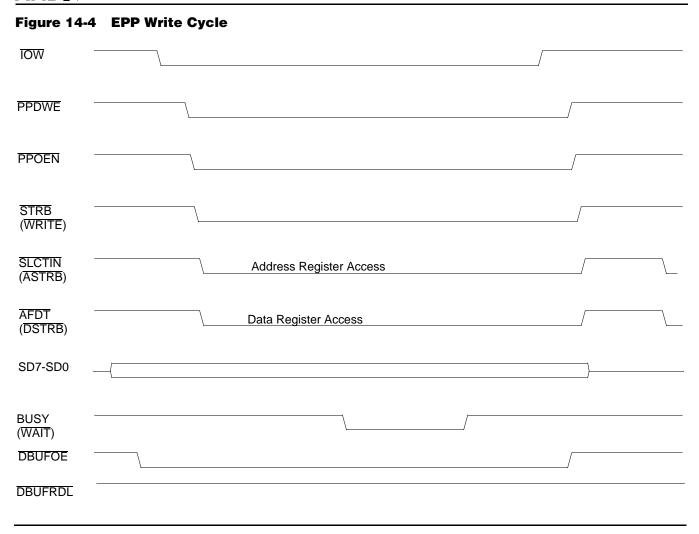

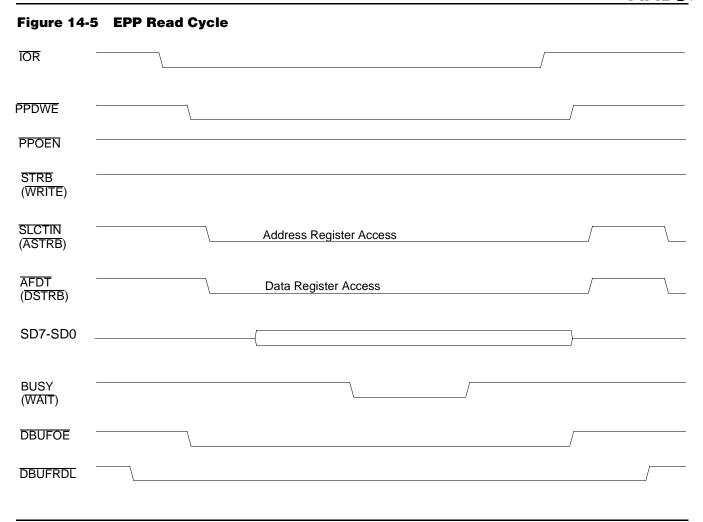

|                                       | 14.5.2.3 Enhanced Parallel Port (EPP) Mode           |      |

|                                       | 14.6 Initialization                                  |      |

|                                       | 14.7 Power Management                                |      |

|                                       | •                                                    |      |

| CHAPTER 15                            | SERIAL PORT (UART)                                   | 15-1 |

|                                       | 15.1 Overview                                        |      |

|                                       | 15.2 Registers                                       |      |

|                                       | 15.2.1 Direct-Mapped Registers                       |      |

|                                       | 15.2.2 Criip Setup and Control (CSC) Index Registers |      |

|                                       | 15.4 Operation                                       |      |

|                                       | 15.4.1 Baud-Rate Generation                          |      |

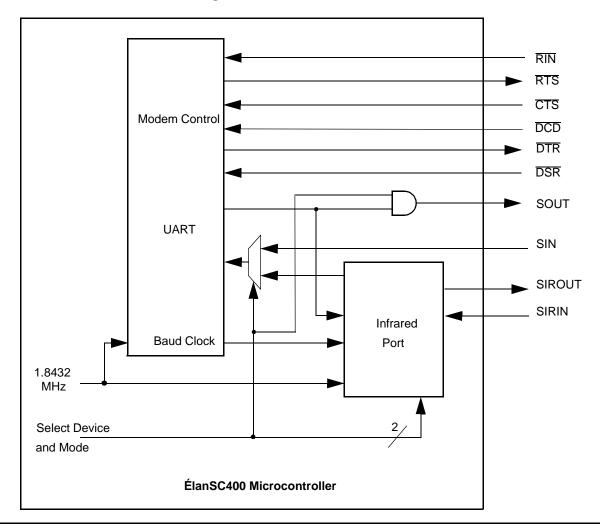

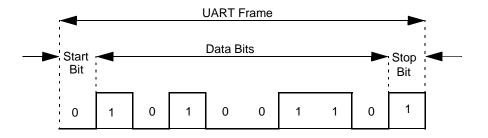

|                                       | 15.4.2 UART Frame                                    |      |

|                                       | 15.4.3 Operating Modes                               |      |

|                                       | 15.4.3.1 16450-Compatible Mode (No FIFOs)            |      |

|                                       | 15.4.3.2 16550-Compatible Mode (FIFOs)               |      |

|                                       | 15.4.4 Interrupts                                    |      |

|                                       | 15.5 Initialization                                  |      |

|                                       | 15.6 Power Management                                | 15-7 |

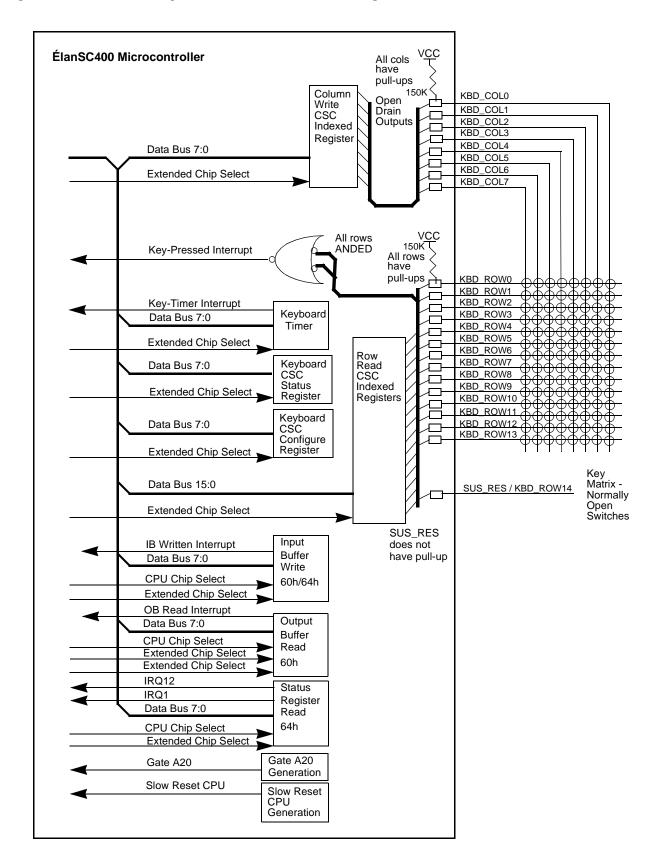

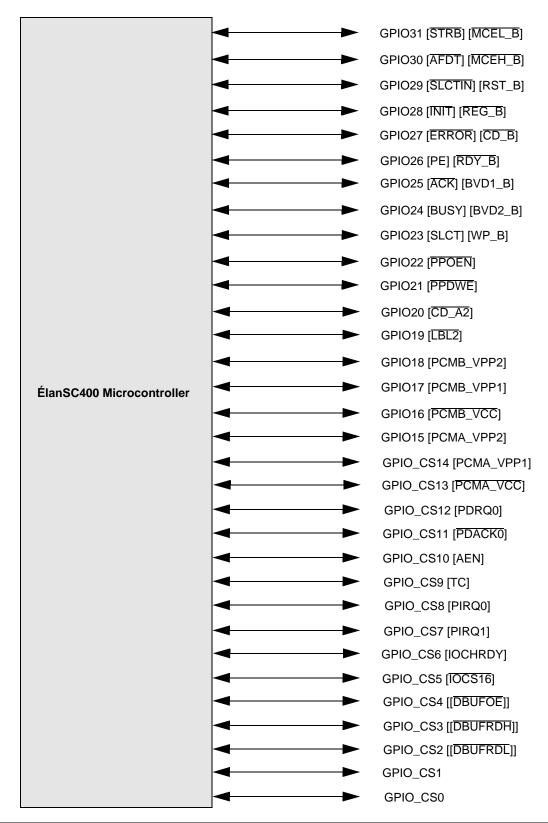

| CHAPTER 10  | KEAROAKI                                                                                                                                                                             | D INTERFACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16-1                                                                   |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

|             | 16.1 Overvie                                                                                                                                                                         | wwe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16-1                                                                   |

|             | 16.1.1                                                                                                                                                                               | Matrix Keyboard Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16-1                                                                   |

|             | 16.1.2                                                                                                                                                                               | SCP Emulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16-2                                                                   |

|             |                                                                                                                                                                                      | XT Keyboard Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                        |

|             |                                                                                                                                                                                      | ers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |

|             |                                                                                                                                                                                      | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |

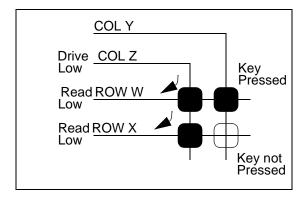

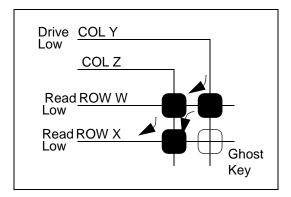

|             |                                                                                                                                                                                      | Matrix Keyboard Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                        |

|             |                                                                                                                                                                                      | 16.3.1.1 N-Key Rollover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                        |

|             |                                                                                                                                                                                      | 16.3.1.2 Key-Pressed Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |

|             |                                                                                                                                                                                      | 16.3.1.3 Keyboard Wake-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                        |

|             |                                                                                                                                                                                      | 16.3.1.4 CPU-Scanned Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                        |

|             |                                                                                                                                                                                      | 16.3.1.5 Keyboard Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                        |

|             |                                                                                                                                                                                      | 16.3.1.6 Typematic Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                        |

|             | 1632                                                                                                                                                                                 | SCP Emulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                        |

|             | 10.0.2                                                                                                                                                                               | 16.3.2.1 SCP GATEA20 and Reset CPU Command Emulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                        |

|             | 1633                                                                                                                                                                                 | Keyboard System Scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                        |

|             | 10.0.0                                                                                                                                                                               | 16.3.3.1 Simple Matrix Keyboard Support by Interrupting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                        |

|             |                                                                                                                                                                                      | 16.3.3.2 Simple Matrix Keyboard Support by Polling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                        |

|             |                                                                                                                                                                                      | 16.3.3.3 Matrix Keyboard Support with PC/AT Compatibility .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                        |

|             | 1634                                                                                                                                                                                 | XT Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                        |

|             | 10.0.1                                                                                                                                                                               | 16.3.4.1 Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                        |

|             |                                                                                                                                                                                      | 16.3.4.2 Enabling the XT Keyboard Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                        |

|             |                                                                                                                                                                                      | 16.3.4.3 Controlling the XT Keyboard Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                        |

|             |                                                                                                                                                                                      | 16.3.4.4 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                        |

|             |                                                                                                                                                                                      | 10.01.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |

|             | 16 4 Initializa                                                                                                                                                                      | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16-13                                                                  |

|             |                                                                                                                                                                                      | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                        |