# Intel386<sup>™</sup> EX Embedded Processor

**Specification Update**

July 1998

**Notice:** The Intel386<sup>™</sup> EX Embedded Processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Order Number: 272873-009

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel386™ EX Embedded Processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

| Revision History             | 5  |

|------------------------------|----|

| Preface                      | 6  |

| Summary Table of Changes     | 8  |

| Identification Information   | 13 |

| Errata                       | 15 |

| Specification Changes        | 40 |

| Specification Clarifications | 43 |

| Documentation Changes        | 44 |

I

# Revision History

The Intel386<sup>TM</sup> EX embedded processor has three production stepping versions. The first stepping, known as 'A' was made available in August, 1994. The second stepping, 'B' has been in production since the beginning of 1995. The B stepping was an interim version to fix the pipelining and some other errata problems found on the A stepping version. C-stepping was made available in early 1996, with C-1 production starting in June, 1996.

The Special Environment Intel386 EX has one production stepping version. The Special Environment 'B' stepping version began production in 1995; production ceased in January, 1998.

**Table 1. Revision History**

| Revision<br>Date | Version | Description                                                                                                                                                                                                         |  |

|------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7/7/98           | 009     | Corrected Documentation Change #1 and added Documentation Change 37.                                                                                                                                                |  |

| 2/23/98          | 008     | Converted to new template. Clarified Errata #39 to apply to autotransmit mode only.                                                                                                                                 |  |

| 9/24/97          | 007     | Added Errata 39 and 40. Added Documentation Changes 33–36.                                                                                                                                                          |  |

| 8/12/97          | 006     | Corrected code sequence in item #5 of Documentation Changes section (page 46).  Added Documentation change 32.                                                                                                      |  |

| 7/21/97          | 005     | Added Specification Change 8 and Documentation changes 30-31.  Corrected code sequence in item #5 of Documentation Changes section (page 46).                                                                       |  |

| 12/23/96         | 004     | Specification Changes IDIV instruction interrupt0 due to overflow                                                                                                                                                   |  |

| 11/11/96         | 003     | Corrected Device and Stepping identifier numbers and added a table to indicate IDCODE identifiers.  Changed Documentation Errata #20 to read "active" in first sentence.  Added Documentation Errata 27, 28 and 29. |  |

| 10/08/96         | 002     | Added Special Environment Errata. Revised Errata 37. Added Specification Changes 5 and 6 (timing errata for EXTB and EXTC devices).                                                                                 |  |

| 9/10/96          | 002     | Added Documentation Changes #5 to #26                                                                                                                                                                               |  |

| 07/23/96         | 001     | Revised timing errata for t34 SMM. Added additional information for errata #37 to clarify boundary conditions. Added note to errata 38 on HOLD signal boundary condition.                                           |  |

| 06/24/96         | 001     | Added timing errata for t34 SMM. Added errata #35, 36, 37, and 38. Included additional documentation changes for Autotransmit.                                                                                      |  |

| 05/01/96         | 001     | This is the new Specification Update document. It contains all identified errata published prior to this date.  Added errata #34                                                                                    |  |

| 07/31/95         | 1.00    | Added errata #1 to #33                                                                                                                                                                                              |  |

### **Preface**

As of July, 1996, Intel's Computing Enhancement Group has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### **Affected Documents/Related Documents**

Table 2. Affected Documents/Related Documents

| Title                                                                                        | Order            |

|----------------------------------------------------------------------------------------------|------------------|

| Intel386™ EX Embedded Microprocessor datasheet                                               | 272420-004, -006 |

| Intel386™ EX Embedded Microprocessor User's Manual                                           | 272485-001, -002 |

| Programming Flash Memory through the Intel386™ EX Embedded Microprocessor JTAG Port (AP-720) | 272753-001       |

| Intel Processor Identification With the CPUID Instruction (AP-485)                           | 241618-003       |

| Special Environment Intel386™ EX Embedded Microprocessor datasheet                           | 271325-003       |

| Intel386™ EX Embedded Microprocessor Evaluation Board Manual                                 | 272525-005       |

| EXPLR1 Embedded PC Evaluation Platform Application Note                                      | 272777-001       |

ı

### **Nomenclature**

**Errata** are design defects or errors. These may cause the published (component, board, system) behavior to deviate from published specifications. Hardware and software designed to be used with any component, board, and system must consider all errata documented.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

Note:

Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

# Summary Table of Changes

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the Intel386 EX product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

### **Codes Used in Summary Table**

### **Stepping**

X: Errata exists in the stepping indicated. Specification Change or

Clarification that applies to this stepping.

(No mark)

or (Blank box): This erratum is fixed in listed stepping or specification change does not

apply to listed stepping.

**Page**

(Page): Page location of item in this document.

**Status**

Doc: Document change or update will be implemented.

Fix: This erratum is intended to be fixed in a future step of the component.

Fixed: This erratum has been previously fixed.

NoFix: There are no plans to fix this erratum.

Eval: Plans to fix this erratum are under evaluation.

Row

Change bar to left of table row indicates this erratum is either new or

modified from the previous version of the document.

### Errata

| Errata | Rev.     | St | teppin | gs |      | 01-1   | FDDATA                                                                                                                    |

|--------|----------|----|--------|----|------|--------|---------------------------------------------------------------------------------------------------------------------------|

| Number | Date     | Α0 | B1     | C1 | Page | Status | ERRATA                                                                                                                    |

| 1      | 07/31/95 | Х  |        |    | 15   | Fixed  | Watchdog Timer (WDT) Bus Monitor Failure<br>During Bus Pipeline Operation                                                 |

| 2      | 07/31/95 | Х  |        |    | 16   | Fixed  | Spurious Slave IR7 Interrupts When Using Internal WDT Interrupt                                                           |

| 3      | 07/31/95 | Х  | Х      |    | 17   | Fixed  | WDT Lockout Sequence May Not Properly<br>Reload Down Counter                                                              |

| 4      | 07/31/95 | Х  |        |    | 17   | Fixed  | WDT Will Time Out During CPU Self-Test                                                                                    |

| 5      | 07/31/95 | Х  | Х      |    | 18   | Fixed  | Timer Generated DMA Requests May Not Initiate Properly After RESET                                                        |

| 6      | 07/31/95 | Х  | Х      |    | 18   | Fixed  | DMA Temporary Register Not Flushed When Software Aborts Transfer                                                          |

| 7      | 07/31/95 | Х  |        |    | 19   | Fixed  | Chip Selects Remain Active During Bus HOLD And DMA Cascade Cycles                                                         |

| 8      | 07/31/95 | Х  | Х      |    | 19   | Fixed  | Write Sequence To Enable Expanded I/O Space Is Not Sequential                                                             |

| 9      | 07/31/95 | Х  | Х      | Х  | 21   | NoFix  | 32-Bit WDT Register Is Oriented As High<br>Word, Low Word In I/O Space                                                    |

| 10     | 07/31/95 | Х  | Х      |    | 21   | Fixed  | Remap Configuration Register At 22H And 23H<br>Have 10-Bit Address Decode                                                 |

| 11     | 07/31/95 | Х  | Х      | Х  | 21   | NoFix  | CAS Lines Do Not Remain Active During Idle<br>States Between Cascaded INTA Cycles                                         |

| 12     | 07/31/95 | Х  | Х      |    | 21   | Fixed  | Cannot Pipeline DMA Bus Cycles                                                                                            |

| 13     | 07/31/95 | Х  | Х      |    | 22   | Fixed  | DSR1#/STXCLK Pin Has A Permanent Weak Pull-Up                                                                             |

| 14     | 07/31/95 | Х  | Х      |    | 22   | Fixed  | READY# Floats In T1 After Internal Bus Cycle Due to LBA#                                                                  |

| 15     | 07/31/95 | Х  |        |    | 22   | Fixed  | Pipelined Bus Operation Does Not Work<br>Reliably, Causing System Problems                                                |

| 16     | 07/31/95 | Х  |        |    | 23   | Fixed  | DMA Registers At Addresses 08H, 09H, And 01AH Do Not Decode 16-Bit Addresses Correctly                                    |

| 17     | 07/31/95 | Х  | Х      |    | 23   | Fixed  | TDO Pin May Float in User Mode Causing Excessive Current Consumption                                                      |

| 18     | 07/31/95 | Х  | Х      |    | 24   | Fixed  | Overflow Enable Bits (TOV0, TOV1, ROV0, ROV1) In DMAOVFE Register Do Not Function as Specified                            |

| 19     | 07/31/95 | Х  | х      | Х  | 24   | NoFix  | Upper DMA Byte Count Registers<br>(DMA0BYC2, DMA1BYC2) Change to 0F0H<br>When the Lower Byte Count Registers<br>Underflow |

| 20     | 07/31/95 | Х  | Х      |    | 24   | Fixed  | At High Baud Rates, There Is Not Enough<br>Time to Turn the Transmitter Off By Resetting<br>the TEN Bit                   |

| 21     | 07/31/95 | Х  | Х      |    | 25   | Fixed  | Write Sequence for WDTCLR Lockout is Not Sequential                                                                       |

### **Errata**

| Errata | Rev.                            | St | Steppings |    | Do   | Status | EDDATA                                                                                                                        |

|--------|---------------------------------|----|-----------|----|------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| Number | Date                            | Α0 | B1        | C1 | Page | Status | ERRATA                                                                                                                        |

| 22     | 07/31/95                        | Х  |           |    | 25   | Fixed  | Setting the Channel Enable Bit (CE) in DMACMD1 Registers also Disables HOLD Requests                                          |

| 23     | 07/31/95                        | Х  |           |    | 25   | Fixed  | DMA Synchronization Problem During<br>Handoffs of Low Priority Channel to High<br>Priority Channel, Resulting in Loss of Data |

| 24     | 07/31/95                        | Х  | Х         |    | 26   | Fixed  | TEN Bit In SSIOCON1 Register Turns Off Transmit Channel Too Soon                                                              |

| 25     | 07/31/95                        | Х  |           |    | 26   | Fixed  | Back-To-Back Writes To Interrupt Controller<br>May Cause Failure In Second Write                                              |

| 26     | 07/31/95                        | Х  |           |    | 27   | Fixed  | DMA And Bus Arbiter Reset May Cause Bus<br>Contention                                                                         |

| 27     | 07/31/95                        | Х  | Х         |    | 28   | Fixed  | Internal HOLD Request Synchronization May Cause Data/Code Fetches To Be Corrupted                                             |

| 28     | 07/31/95                        | Х  | Х         | Х  | 28   | NoFix  | Writing To One DMA Channel's Register When A Request From The Other Channel Occurs May Cause An Improper Transfer.            |

| 29     | 07/31/95                        | Х  | Х         |    | 28   | Fixed  | Insufficient Address Hold Time After WR#<br>Goes High                                                                         |

| 30     | 07/31/95                        | Х  | Х         |    | 29   | Fixed  | HLDA Inactive To HOLD Active Arbitration<br>Could Improperly Float The Bus                                                    |

| 31     | 07/31/95                        | Х  | Х         |    | 30   | Fixed  | FLT# Does Not Float All Outputs                                                                                               |

| 32     | 07/31/95                        | Х  | Х         |    | 31   | Fixed  | SIO Break Could Be Missed                                                                                                     |

| 33     | 07/31/95                        | Х  | Х         |    | 31   | Fixed  | Arbitration Between Powerdown And Refresh<br>Cycles May Leave Control Signals In Wrong<br>State                               |

| 34     | 05/01/96                        |    | Х         |    | 31   | Fixed  | Refresh Control With More Than 2 Wait States<br>Could Cause An Erroneous Bus Cycle                                            |

| 35     | 06/24/96                        | Х  | Х         | Х  | 32   | No Fix | Internal READY# Generation Switching from Non-pipeline to Pipeline Can Be Temporarily Asserted                                |

| 36     | 06/24/96                        |    |           | Х  | 32   | No Fix | NA# Must Not Be Asserted In A T2P State for DMA Pipelining                                                                    |

| 37     | 07/23/96                        |    |           | Х  | 33   | No Fix | Arbitration for HOLD During Refresh Cycle<br>May Not Return an HLDA Signal                                                    |

| 38     | 07/23/96                        |    |           | Х  | 37   | No Fix | READY# Source Conflicts May Cause Bus<br>Cycle Failure                                                                        |

| 39     | 09/25/97<br>Updated:<br>2/26/98 |    |           | х  | 38   | No Fix | Not All Baud Rates from Baud-rate Generator<br>Operate Correctly                                                              |

| 40     | 09/25/97                        |    |           | Х  | 39   | No Fix | With Autotransmit Enabled, the First Bit Is<br>Transmitted at the Wrong Baud Rate                                             |

## **Specification Changes**

| Change | ge Revision Steppings | Page | Page Status | SPECIFICATION CHANGES |      |        |                                                                       |                       |

|--------|-----------------------|------|-------------|-----------------------|------|--------|-----------------------------------------------------------------------|-----------------------|

| Number | Date                  | Α0   | В1          | C1                    | raye | Status | rage Status                                                           | SPECIFICATION CHANGES |

| 1      | 06/24/96              |      | Х           |                       | 40   | Doc    | AC Timings Modified for 5V +/-0.5V                                    |                       |

| 2      | 06/24/96              |      | Х           |                       | 40   | Doc    | AC Timings for modified for 3.3V +/-0.3V                              |                       |

| 3      | 06/24/96              |      | Х           |                       | 41   | Doc    | AC Timings for 3.0V +/-0.3V                                           |                       |

| 4      | 07/23/96              |      |             | Х                     | 41   | Doc    | AC Timings for T34 on EXTB and EXTC devices is different when in SMM. |                       |

| 5      | 10/08/96              |      |             | Х                     | 41   | Doc    | AC Timings Modified for EXTB Device                                   |                       |

| 6      | 10/08/96              |      |             | Х                     | 42   | Doc    | AC Timings Modified for EXTC Device                                   |                       |

| 7      | 12/23/96              | Х    | Х           | Х                     | 42   | Doc    | IDIV Instruction Interrupt0 Due To Overflow                           |                       |

| 8      | 7/21/97               |      |             | Х                     | 42   | Doc    | FLT# Pin Should be Pulled Up to VCC                                   |                       |

### **Specification Clarifications**

| Rev. Date | Steppings |    | Page | Status | SPECIFICATION CLARIFICATIONS |                                                      |

|-----------|-----------|----|------|--------|------------------------------|------------------------------------------------------|

| Nev. Date | Α0        | B1 | C1   | rage   | Otatas                       | SI ESII ISATISN SEANII ISATISNS                      |

|           |           |    |      |        |                              | None for this revision of this specification update. |

### **Documentation Changes**

| Change<br>Number | Revision<br>Date | Page | DOCUMENTATION CHANGES                                                                                                                                                        |

|------------------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                |                  | 44   | 272485-001, Correct Latching Of BS8# In Reference To 8 Bit Vs. 16 Bit Device Access (Modified on 7/7/98)                                                                     |

| 2                |                  | 45   | 272485-001, Programming One Or Both Channels of the DMA Requires Both Channels To Be Masked. DMA Channels Must Also Be Masked While Reading/Writing To DMA Related Registers |

| 3                |                  | 45   | 272420-006, Values for ICC Represent the Maximum Supply Currents with the Device Held In Reset and Inputs Pulled to Their Inactive Levels                                    |

| 4                |                  | 45   | 272485-002, Autotransmit Mode for SSIO Requires Baud Rates Above 3.2 MHz                                                                                                     |

| 5                |                  | 46   | 272485-002, Section 4.5.2.1, Page 4-8, Figure 4-4.                                                                                                                           |

| 6                |                  | 46   | 272485-002, Section 4.6.4, Page 4-13, Figure 4-7.                                                                                                                            |

| 7                |                  | 46   | 272485-002, Section 5.3, Page 5-27, Figure 5-18.                                                                                                                             |

| 8                |                  | 46   | 272485-002, Section 6.2.4, Page 6-11.                                                                                                                                        |

| 9                |                  | 47   | 272485-002, Section 6.3.1, Page 6-13.                                                                                                                                        |

| 10               |                  | 47   | 272485-002, Section 6.3.6, Page 6-29, Figure 6-11.                                                                                                                           |

| 11               |                  | 47   | 272485-002, Section 6.3.6, Page 6-30, Figure 6-12.                                                                                                                           |

| 12               |                  | 48   | 272485-002, Section 6.6.1.2, Page 6-40, code example.                                                                                                                        |

| 13               |                  | 48   | 272485-002, Section 6.6.4, Page 6-43.                                                                                                                                        |

## **Documentation Changes**

| 14 | 48 | 272485-002, Section 9.3.4, Page 9-21.              |

|----|----|----------------------------------------------------|

| 15 | 48 | 272485-002, Section 12.3, Page 12-28, Table 12-3.  |

| 16 | 48 | 272485-002, Section 12.3.11, Page 12-44.           |

| 17 | 48 | 272485-002, Section 12.3.13, Page 12-47.           |

| 18 | 48 | 272485-002, Section 13.2.2.2, Page 13-12.          |

| 19 | 48 | 272485-002, Section 15.5, Page 15-12.              |

| 20 | 48 | 272420-006, Section 7.0, Page 25.                  |

| 21 | 49 | 272753-001, Figure 2, Page 7.                      |

| 22 | 49 | 271325-003, Section 1.0, Pages 2-3.                |

| 23 | 49 | 271325-003, Section 1.0, Pages 5-6.                |

| 24 | 49 | 272485-002, Appendix A, Page A-10.                 |

| 25 | 49 | 272485-002, Section 5.2.6, Page 5-20, Figure 5-12. |

| 26 | 49 | 272525-005, Appendix C, Page C-1                   |

| 27 | 49 | 272485-002, Section 13.2.2.1, Page 13-9            |

| 28 | 51 | 272485-002, Section 13.2.2.2, Page 13-12           |

| 29 | 51 | 272485-002, Section 14.6, Page 14-22               |

| 30 | 51 | 272420-006, Page 9, Table 4                        |

| 31 | 52 | 272420-006, Page 12, Table 4                       |

| 32 | 52 | 272485-002, Page 14-3, Note                        |

| 33 | 52 | 272485-002, Page 9-3, Figure 9-1                   |

| 34 | 52 | 272485-002, Section 13.2.1, Page 13-5              |

| 35 | 52 | 272753-001, Table 3, Page 6.                       |

| 36 | 53 | 272485-002, Section 13.2.1, Page 13-12             |

| 37 | 53 | 272777-001, Table 9, Page 20                       |

|    |    |                                                    |

I

### Identification Information

### **Markings**

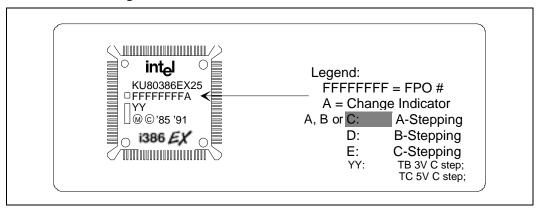

C-stepping production devices are marked with a *change indicator* 'E'. The B-stepping production devices are designated with a 'D' and the A-stepping production version of the Intel386 EX is designated with a change indicator of 'A', 'B', or 'C'. Figure 1 is an illustration indicating where the change indicator marking is located on the package markings. The change indicator is used to relate information found here, and in other documents like datasheets, to a specific device.

**Figure 1. Commercial Markings**

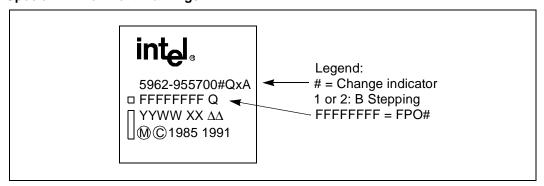

The B-stepping production version of the Special Environment Intel386 EX is designated with a change indicator of '1' or '2'. Figure 2 is an illustration indicating where the change indicator marking is located on the package markings. The change indicator is used to relate information found here, and in other documents like datasheets, to a specific device.

Figure 2. Special Environment Markings

If there is not an FPO# line on the device — hence, no change indicator — but is marked with a Qxxxx (where x=any digit) on the second line, it is likely a pre-production sample part. Consult your Intel representative if you are unclear on the device stepping.

Intel386 EX processors may be identified electrically according to device type and stepping. Refer to the datasheet for instructions on how to obtain the identifier number.

| Device and Stepping | Identifier in DX |

|---------------------|------------------|

| 80386EX A0          | 2309H            |

| 80386EX B1          | 2309H            |

| 80386EX C1          | 2309H            |

Refer to the datasheet for instructions on how to obtain identifier numbers. Another source is the *Intel Processor Identification With the CPUID Instruction* Application Note number AP-485.

#### JTAG registers

Intel provides a copy of the Boundary-Scan-Description-Language file for the A stepping of the Intel386<sup>TM</sup> EX Embedded Processor on the BBS, at (916) 356-3600. This file lists:

- The physical pin layout of all pins in the Boundary Scan Register

- The valid and reserved JTAG unit opcodes

- The expected contents of the IDCODE register for the Intel386 EX Embedded Processor

- A description of the BSR contents

The BSDL file may be incorporated into software which uses the JTAG port for testing or programming functions.

| Device and Stepping | Identifier in IDCODE |

|---------------------|----------------------|

| 80386EX A0          | 00270013H            |

| 80386EX B1          | 00270013H            |

| 80386EX C1          | 3V: 20270013H        |

| OUSODEX CT          | 5V: 28270013H        |

### Errata

#### 1. Watchdog Timer (WDT) Bus Monitor Failure During Bus Pipeline Operation

Problem:

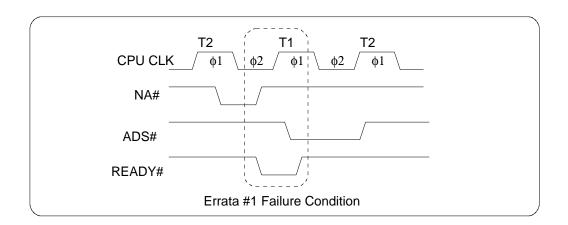

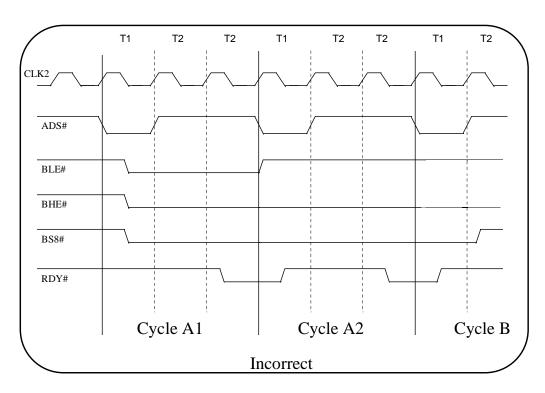

The errata applies to the WDT unit when using the Bus Monitor Mode and Bus Pipeline operation. If a pipelined bus cycle is requested at the same time the current bus cycle is completed, the WDT down counter is not reloaded or stopped. This condition means that the WDT could time-out and erroneously report a system failure. The waveform below shows the errant condition.

The errata condition is caused by the system generating READY# immediately after NA# has been requested, and a T1 cycle is generated (rather than a T2P cycle). Essentially, the system is requesting a pipelined access, but does not need it because READY# has been returned. Such a condition is not typically expected when using the pipeline feature.

Implication:

Applications that use the bus monitor mode of the WDT need to be aware of this condition. If bus pipelining is not used, the errata can be ignored. If bus pipelining is used, look to the workaround description below to ensure the errata condition is avoided.

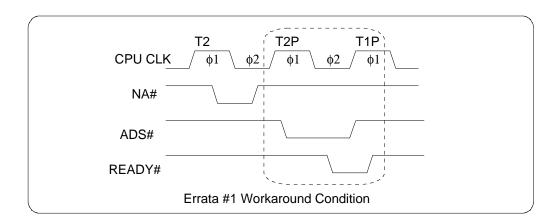

Workaround:

Ensure that READY# is not generated after a pipelined bus operation is requested. See the example waveform below.

**Status:** Corrected on B stepping. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 2. Spurious Slave IR7 Interrupts When Using Internal WDT Interrupt

Problem:

The WDT interrupt signal (WDTOUT) to the ICU does not remain active until the interrupt is acknowledged by the CPU (valid INTA cycle), resulting in the generation of a spurious IR7 request on the slave interrupt controller.

An interrupt request must remain active until the CPU has acknowledged the interrupt, at which time the request is latched, the appropriate in-service bit is set, and the vector type is read. If an interrupt is generated, but removed before the CPU has acknowledged it, the interrupt controller returns a default IR7 vector type and does not set any in-service bits. It is then the responsibility of the IR7 interrupt service routine to check the IR7 in-service bit and determine if a valid (in-service bit set) or spurious (in-service bit cleared) interrupt has occurred. However, since the WDTOUT is connected to the IR7 input of the slave interrupt controller, it is not possible to determine if the WDT or another interrupt generated the spurious interrupt.

Implication:

This errata applies to those applications that typically use the WDTOUT as a general purpose counter and wish to generate interrupts when the counter times out. The application software needs to handle the case that both WDT interrupts and spurious interrupts will be reported the same way.

Workaround:

The WDT interrupt to the slave interrupt controller is an internal signal and cannot be modified by the user. Therefore it is not possible to remove the error condition from a hardware perspective. The slave IR7 interrupt service routine must be written to handle both WDT interrupts and spurious interrupts without the assistance of the in-service bit.

One possible way to determine if the WDT generated the interrupt would be to test the WDT counter value. Since the WDT counter reloads when the WDT count expires (i.e., reaches zero), then comparing the current WDT counter value to the reload value may indicate that the WDT expired and generated the interrupt. Of course, since the WDT counter decrements every two CLK2 periods, the WDT counter and the reload counter will never be the same. Thus, such a test as mentioned here would have to account for a possible range of values (i.e., the WDT counter is less than some percentage value of the reload counter).

Additionally, if an external interrupt pin is available the WDTOUT pin can always be connected to it through an external inverter to provide the WDT interrupt.

Status:

Corrected on B stepping. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 3. WDT Lockout Sequence May Not Properly Reload Down Counter

**Problem:** If the WDT is in general timer mode or bus monitor mode, and the CLKDIS bit is set (i.e., counter

is stopped), enabling the system watchdog mode by executing the lockout sequence does not reload the down counter. This means the counter will start counting down from whatever the previous

value was in the counter (rather than starting from the value in the reload counter).

**Implication:** Since the WDT is reset to general timer mode with the CLKDIS bit cleared, this errata applies to an

application that disables the WDT before it enables the system watchdog mode.

Workaround: There are two possible workarounds. Executing two lockout sequences will reload the counter

correctly. Essentially the first lockout sequence enables the WDT, while the second sequence reloads the counter. Another workaround that requires less code is to enable the counter first by clearing the CLKDIS bit, and then execute the lockout sequence (see code example below).

```

MOV

DX, WDTSTATUS

; Read WDT status register

IN

AL, DX

AND

AX, OFCH

; Clear clock dis/bus mon bits

OUT

DX, AL

; Update register

MOV

DX, WDTCLR

MOV

AX, OF01EH

DX, AX

OUT

AX, OFE1H

VOM

OUT

DX, AX

; Lockout Sequence

```

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

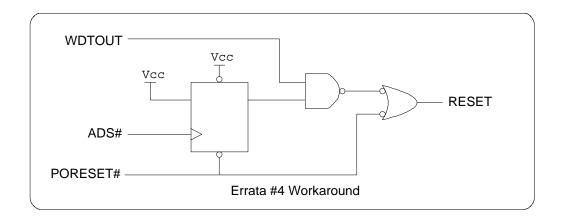

#### 4. WDT Will Time Out During CPU Self-Test

Problem: When entering CPU self-test mode (BUSY# low when RESET goes low), the WDT counter is

loaded with the value 0000FFFFH (65,535). However, it takes over 1,048,575 (000FFFFFH) clocks to complete an internal self-test, meaning the WDT will have timed out prior to completing

a CPU self-test.

Implication: This errata only applies to a system design that uses the WDTOUT signal to generate a device

reset. The WDT will time out and reset the device before the CPU self-test can complete.

Workaround: The WDTOUT signal cannot be directly tied to the RESET input during self-test since there is no

mechanism to increase the default value loaded into the WDT counter. The circuit shown below can be used to block WDTOUT until the first ADS# is generated. The signal PORESET# is a power-on reset signal generated by the system. WDTOUT is an output of the Intel386 EX processor, and RESET is an input to the processor. Please note that the circuit below has not been

tested in a real design and is provided as an example only.

Status: Corrected on B stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

#### 5. Timer Generated DMA Requests May Not Initiate Properly After RESET

**Problem:** The internal signal paths between the Timer Control Unit (TCU) outputs and the DMA Control

Unit request inputs contain a flip-flop that may not be properly initialized after a device reset (i.e., the output of the flip-flop may be high or low). This means that a TCU DMA request may be present prior to the timer actually generating the request. The errata applies to both DMA timer

requests.

Implication: This errata only affects DMA requests generated by the TCU. If the TCU is configured to

generated DMA requests, the initialization software must ensure the TCU DMA request bit is

cleared.

Workaround: Before programming the TCU, and after programming the DMA configuration register, the DMA

status register can be read to determine if a timer request is already pending (errata condition). If the request is pending, a dummy timer DMA operation must be initiated prior to using the TCU for DMA requests (after one DMA cycle, the flip-flop will be properly initialized). If the request is not pending, the errata condition does not apply and the dummy DMA cycle does not need to be run.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

#### 6. DMA Temporary Register Not Flushed When Software Aborts Transfer

**Problem:** During two-cycle DMA operation, should the channel's transfer be aborted before terminal count is

reached or EOP# is generated, the data in the temporary register is not flushed. When the channel is reprogrammed, the old data in the temporary register will be transferred to the new destination

address.

**Implication:** This errata applies to two-cycle transfers only, and not fly-by transfers (since the temporary buffer

is not used in fly-by transfers). If the application terminates a DMA transfer by disabling the DMA channel, it is possible that not all of the data has been transferred from the temporary buffer and

will be unexpectedly inserted into the next DMA transfer.

Workaround: DMA transfers must terminate using TC or EOP# only. It is not possible to flush the temporary

registers in software.

Status: Corrected on the C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

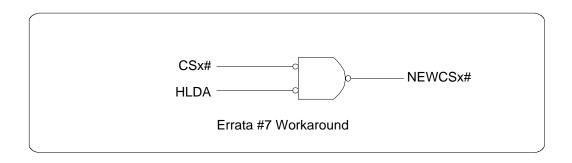

7. Chip Selects Remain Active During Bus HOLD And DMA Cascade Cycles

**Problem:** When the device enters a bus HOLD state because of a HOLD or DMA Cascade operation, the

Chip Select that was valid in the previous cycle can remain active during the bus hold. This can

cause bus contention when another bus master gains control of the bus.

**Implication:** This errata only applies to those applications which cause the bus to enter a bus hold state and the

assertion of a chip-select can cause bus contention.

Workaround: Qualify a chip-select with HLDA such as shown in the circuit below. The chip-select will go

inactive if HLDA goes active. If using a PLD device, then HLDA should be used to qualify the

chip-select as shown in the following diagram.

**Status:** Corrected on B stepping. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 8. Write Sequence To Enable Expanded I/O Space Is Not Sequential

Problem:

The I/O write sequence to enable expanded I/O space does not have to be executed back-to-back. Any other I/O address or I/O address sequence can occur during the sequence and will not affect the enabling of expanded I/O space. This departs from the original design intent that if the sequence is not followed exactly, it must be repeated from the beginning.

Consider the sequence to enable expanded I/O space as a sequence of states shown below:

```

Start at State A (expanded I/O space Disabled)

MOV

AX, 8000H

;Writing 00 to byte I/O

OUT

23, AL

;address 23H gets to state B

;Writing 80H to byte I/O

XCHG

AL, AH

OUT

22H, AL

;address 22H gets to state C

22H, AX

;Writing 0080H to word I/O

OUT

; address 22H gets to state D,

; which enables Expanded I/O space.

```

Each write to I/O space with the appropriate data value in AL moves the internal state machine from one state to the next. Thus the sequence of going from State A to State B, State B to State C, and State C to State D enables expanded I/O space. Anything can happen between the states shown above, and the sequence is not interrupted (i.e., reset back to State A).

To make the device more secure and avoid inadvertently enabling the ESE bit, the C-step device state machine requires a sequential back-to-back write. State machine security will not allow software to enable I/O out of sequence. If the sequence is not followed, the internal state machine must be started in the Reset state A to assure proper enabling of the ESE bit. The code sequence below assures the proper advancement of states:

```

Disable interrupts to avoid unexpected state machine

; reset due to I/O within an interrupt handler

CLI

;Disables interrupts

; Start at Reset state (expanded I/O space Disabled)

ΙN

AL, 23H

; Resets state machine (Reset=State A)

MOV

AX, 8000H

;Clears ESE bit

OUT

23H, AL

;First unlock sequence, moves

;state machine to state B

AL, AH

XCHG

;Writing 80H to byte I/O

OUT

22H, AL

; Second unlock seequence, moves

;state machine to state C

OUT

22H, AX

;Third unlock sequence, moves

istate machine to state D, sets ESE

;bit, which enables Expanded I/O space

; Will re-enable interrupts, if desired

STI

```

#### Implication:

The software writer must assume that the writes have to be back-to-back and disable interrupts during the successive writes. This should not impact B step designs if the recommended programming techniques were used. It may be necessary to add instructions for C-step designs, if the back-to-back sequence was not followed in the software. Disabling interrupts and resetting the internal state machine will assure the write sequence enables the ESE bit. Software instructions used to clear the ESE bit can advance the state machine to State B if the instruction match is OUT 23H, AL. To properly enable expanded I/O space as desired, insert the line IN AL, 23H before beginning the unlock sequence.

#### Workaround:

None. The application software must be aware that the I/O write sequence is not reset if any other I/O writes occur during the sequence. Note however, that code should be written assuming the sequence does need to be back-to-back. This will ensure proper operation if the errata is fixed in a future stepping.

#### Status:

Correct on C-stepping. Refer to Summary Table of Changes to determine the affected stepping(s).

9. 32-Bit WDT Register Is Oriented As High Word, Low Word In I/O Space

**Problem:** The 32-bit counter register and reload register are located with the high word located at a lower I/O

address space than low word. As a result, 32-bit I/O accesses to these registers will have high and low words swapped, making it impossible to write a 32-bit value directly to the counter and reload

registers.

**Implication:** This errata only applies to system software that maintains a 32-bit image of the WDTRLD and

WDTCNT registers in memory and wishes to perform a 32-bit register move to I/O address space.

**Workaround:** The memory or register image must swap the low-word and high-word values to perform a 32-bit

register move to the I/O registers.

**Status:** No fix is planned. Refer to Summary Table of Changes to determine the affected stepping(s).

10. Remap Configuration Register At 22H And 23H Have 10-Bit Address Decode

Problem: When expanded I/O space is not enabled, only the lower 10-bits of I/O addresses are used to

decode the internal peripherals and the configuration registers at 22H and 23H. This means that the configuration registers will appear in I/O space at every 1K address boundary (for example, 22H,

1022H, 2022H, etc.).

**Implication:** This errata affects those applications which may place system peripherals in I/O address space that

didn't expect registers 22H and 23H to repeat every 1K block. The access to I/O locations such as 1022H will be decoded internally and generate a 1 wait internal access. Depending on the value

written, it could possibly enable expanded I/O address space (see errata #8).

Workaround: Enable expanded I/O space to turn on 16-bit decode when communicating with I/O devices that

overlap 22H and 23H at I/O addresses above 1K. This means that the internal peripherals are

decoded using all 16-bit of the I/O address.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

11. CAS Lines Do Not Remain Active During Idle States Between Cascaded

**INTA Cycles**

**Problem:** The interrupt controller CAS lines do not maintain a valid value during the four idle states between

the first INTA cycle and the second INTA cycle (assumes an externally cascaded device is present). The three CAS lines (CAS0-CAS2) are OR'd with address lines A16-A18. During the first INTA bus cycle, these line drive out the cascade address which is decoded by the slave interrupt controller to determine if it must place the vector type on the bus during the second INTA. There are four idle states automatically inserted between the end of the first INTA bus cycle and the start of the second INTA bus cycle. During these idle states, the CAS lines revert back to address mode and are driven high (logic 1), which will cause problems for the external interrupt

controller.

Implication: This errata only applies to those applications that expand interrupts using an external 8259A

Programmable Interrupt Controller device as slave interrupt controllers.

**Workaround:** The CAS lines must be latched and preserved throughout both of the INTA bus cycles.

**Status:** No fix is planned. Refer to Summary Table of Changes to determine the affected stepping(s).

12. Cannot Pipeline DMA Bus Cycles

**Problem:** During a DMA bus cycle, NA# does not function properly with the DMA unit.

**Implication:** This errata affects systems that make use of pipeline bus operation and the DMA controller.

**Workaround:** None. Do not use address pipelining when using the integrated DMA controller.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

13. DSR1#/STXCLK Pin Has A Permanent Weak Pull-Up

Problem: The weak pull-up device used to hold the state of the DSR1#/STXCLK pin at a high level until

device configuration is complete does not turn off. This condition results in a higher than normal

leakage current for the pin.

Implication: This errata applies to all applications.

Workaround: None. The external driver must be strong enough to pull down the pin. The weak pull-up is approx-

imately 5 KOhms.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

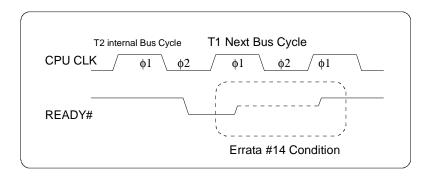

#### 14. READY# Floats In T1 After Internal Bus Cycle Due to LBA#

Problem: During internal bus cycles, the LBA# signal does not remain active into the next T1 bus state,

causing READY# to float during T1. This is unlike bus cycles controlled by the Chip Select Unit

(CSU), where READY# is driven inactive during T1 of the next bus cycle.

Implication: This errata applies to all applications.

Workaround: Pull-up READY# if the float condition will cause system logic to operate improperly.

Status: Corrected on C-stepping. LBA# description has been documented in the User's Manual to reflect

proper operation. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 15. Pipelined Bus Operation Does Not Work Reliably, Causing System **Problems**

Problem:

Some of the internal peripherals (such as the Interrupt Control unit) are responsible for decoding the various bus states (e.g., T1, T2) and bus cycles (e.g., I/O read, Halt) to determine if some action

on their part is necessary. For example, the Interrupt Control unit decodes INTA bus cycles and determines if it should drive a vector type on the bus during the T2 bus state. Bus states consist of T1, T2, Ti, Th, T1P, T2P, and T2i. Refer to any of the Intel386<sup>TM</sup> processor manuals for information on bus states. Bus cycles are decoded from the three control lines M/IO#, W/R#, and

D/C#.

These same peripherals, however, are blocked from responding from bus cycles during special bus states, such as IDLE (Ti) and HOLD (Th), where bus cycle information is unknown or

indeterminate. Unfortunately, some of the peripherals were not blocked from pipeline idle, or T2i, states. This means it is possible for a peripheral unit, the Interrupt Controller for example, to

incorrectly decode bus cycles during a T2i state and perform an operation that is unintentional. T2i bus state occurs during pipelined bus cycles when NA# has been asserted and there is no internal CPU request pending.

All of the peripherals correctly respond to Ti (idle) and Th (hold) bus states, meaning that normal (non-pipelined) operation works correctly. If pipeline bus operation is utilized, then it is possible for peripherals like the Interrupt control unit to begin to behave incorrectly should a T2i state occur. For example, if the three control lines (M/IO#, W/R#, D/C#) all go to a low state during a T2i state, the Interrupt Controller decodes this to mean that an INTA cycle is in progress and responds accordingly. This may cause the processor to be in a state where pending interrupts are seemingly ignored.

The Interrupt Control unit is just one example of where a system failure can result due to the execution of a T2i bus state. There is no way to guarantee, or even tell what state the three control lines will be driven to in a T2i bus state, thus it is not possible to define all conditions (sequences of bus states) that will cause one problem or another, or no problem at all.

**Implication:** All applications that make use of pipelined bus operation are affected.

**Workaround:** Tie NA# high and do not use pipelined bus operation.

Status: Corrected on B stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

16. DMA Registers At Addresses 08H, 09H, And 01AH Do Not Decode 16-Bit Addresses Correctly

Problem: The I/O address decoders used for the DMA registers at I/O addresses 08H, 09H, and 01AH do not

decode 16-bit addresses correctly. Accesses to registers or I/O peripherals mapped into 1 kilobyte multiples (0408H, 0808H, etc.) of the DMA register addresses will cause unexpected accesses to the DMA registers. Note that in the chip select unit CS1# and CS3# have registers which are mapped into addresses F408H, F409H, and F41AH. These chip selects will be impacted by this

errata.

**Implication:** This errata applies to all applications that make use of the DMA unit.

Workaround: Do not map external I/O peripherals into addresses that are at 1K multiples of the DMA register

addresses. For the two chip selects that are affected by this errata it is important to initialize the chip selects and then immediately set up the DMA channels, in that sequence. Very few applications will need to modify the contents of the chip select registers after initialization, but for those

that do it will be necessary to re-initialize the affected DMA registers.

Status: Corrected on B stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

17. TDO Pin May Float in User Mode Causing Excessive Current Consumption

**Problem:** The TDO pin usually floats in user mode. This could turn on the unused input buffer at the pin

resulting in high leakage current.

**Implication:** This errata applies to all applications that utilize the idle or power down modes, or that are sensitive

to small increases in Icc due to leakage current.

**Workaround:** Put a weak pull-up resistor on the TDO pin.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

18. Overflow Enable Bits (TOV0, TOV1, ROV0, ROV1) In DMAOVFE Register Do Not Function as Specified

**Problem:** The overflow enable bits in DMA register DMAOVFE do not match the definition. TOV1 and

TOV0 control Requester Address and Byte Count registers. They should control Target Address and Byte Counter registers. ROV1 and ROV0 control Target Address registers. They should

control Requester Address registers.

**Implication:** This errata applies to all applications that utilize the DMA controller. Note that it will only affect

those applications that require the TOV bit to be set to a different value than the ROV bit.

**Workaround:** The application must be aware that the register bit functions are reversed from the definition given

and account for that in software.

Status: Corrected on C-stepping. With this workaround, the application must be changed when a

conversion to C-step is initiated. However, this will only impact applications requiring the TOV bit to be set to a different value than the ROV bit. Refer to Summary Table of Changes to determine

the affected stepping(s).

19. Upper DMA Byte Count Registers (DMA0BYC2, DMA1BYC2) Change to 0F0H When the Lower Byte Count Registers Underflow

**Problem:** In the DMA when the overflow enable bit is not set for the Byte counter (only 16-bits of byte

counter are being used), the upper byte count register, DMA0BYC2 or DMA1BYC2, is changed to

0F0H whenever the lower register underflows.

**Implication:** This errata applies to all applications that utilize the DMA controller.

Workaround: This errata will not impact the operation of the DMA controller. The user should be aware,

however that if the application requires the DMA to switch from 8237A mode to its enhanced mode (using all 24 bits of byte count) then the high byte count registers may not contain the reset

value of 00H and should be re-initialized.

**Status:** No fix is planned. Refer to Summary Table of Changes to determine the affected stepping(s).

20. At High Baud Rates, There Is Not Enough Time to Turn the Transmitter Off

By Resetting the TEN Bit

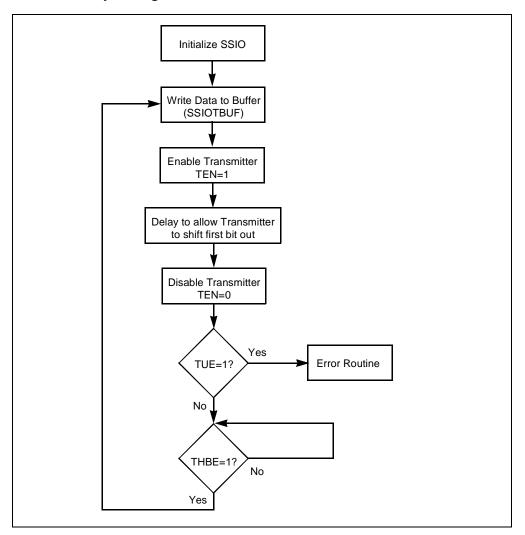

**Problem:** The SSIO transmitter is turned off by clearing the TEN bit in the SSIOCON1 control register. In

the case where the SSIO is transmitting at high baud rates (i.e., the DMA is being used to service the transmitter) it is possible that there is not enough time for the processor to clear the TEN bit between when a THBE (transmit holding buffer empty) interrupt occurs and when the previous word is completely shifted out of the shift register. This is due to interrupt latency time. The result is that it is possible for the last word of a transmission to be shifted out of the shift register more than once. The baud rate at which this starts to become a problem depends on the frequency the processor is running at, the mode (real or protected) it is running in, and any other factors which

may affect interrupt latency.

**Implication:** This errata applies to all applications that require non-continuous high speed synchronous serial

transfers.

Workaround: This errata will limit how fast the SSIO transmitter can operate. Since the baud rate will be limited

by interrupt latency, this can be calculated using the instruction execution/interrupt latency information given in the *Intel386<sup>TM</sup> SX Processor Programmer's Reference Manual* or *Intel386<sup>TM</sup>*

SX Processor Hardware Reference Manual.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

21. Write Sequence for WDTCLR Lockout is Not Sequential

**Problem:** The I/O write sequence to WDTCLR to do the lockout does not have to be executed back-to-back.

An access to any I/O address or I/O address sequence except for another WDT register can occur during the sequence and will not affect the lockout of the watchdog timer. This departs from the original design intent that if the sequence is not followed, it must be repeated from the beginning. The sequence will abort only if a write to another WDT register is made before the second write to

WDTCLR.

**Implication:** The software writer must assume that the I/O writes have to be back-to-back. This should not

impact B-step designs if the recommended programming techniques were used.

**Workaround:** None, as the application software must be aware that the I/O write sequence is not reset if any other

I/O writes occur during the sequence. Note however, that code should be written assuming the sequence does need to be back-to-back. This will assure proper operation if the errata is fixed in a

future stepping.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

22. Setting the Channel Enable Bit (CE) in DMACMD1 Registers also Disables

**HOLD** Requests

Problem: The Channel Enable (CE) bit in the DMACMD1 control register is used to globally disable

requests from both channels of the DMA controller to the bus arbiter. However, it not only disables

requests from the DMA channels, but also from the HOLD pin.

**Implication:** This errata applies to all applications that require disabling of the DMA unit.

Workaround: When both channels of the DMA controller are not needed they should be disabled using either the

Individual Channel Mask Register - DMAMSK, or the Group Channel Mask Register -

DMAGRPMSK.

Status: Corrected on B stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

23. DMA Synchronization Problem During Handoffs of Low Priority Channel to

High Priority Channel, Resulting in Loss of Data

**Problem:** Between the DMA logic and the DMA state machine is a problem that manifests itself if the bus

arbiter changes which channel with an active request has the highest priority, and at the same instant asserts XFRREQ (transfer request). If the bus arbiter receives a DMA request on a channel that has a lower priority, it will activate an enable channel signal to the DMA, and request the bus from the core. If a request comes in on a higher channel, the bus arbiter will then deselect the channel with a lower priority, and select the channel with the higher priority. If conditions are right, the bus arbiter can deselect the lower priority channel, select the higher priority channel, and give

the DMA XFRREQ (transfer request) simultaneously.

**Implication:** This errata applies to all applications that use both DMA channels. This problem appeared specifi-

cally when the DMA priority was set to its default value (i.e., DMA0 has higher priority over

DMA1).

**Workaround:** Change the default DMA priority by writing 00h to DMACMD2 register, and always use DMA1 as

the higher priority channel.

Status: Corrected on B stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

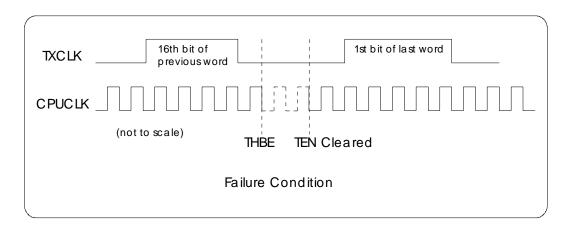

#### 24. TEN Bit In SSIOCON1 Register Turns Off Transmit Channel Too Soon

Problem:

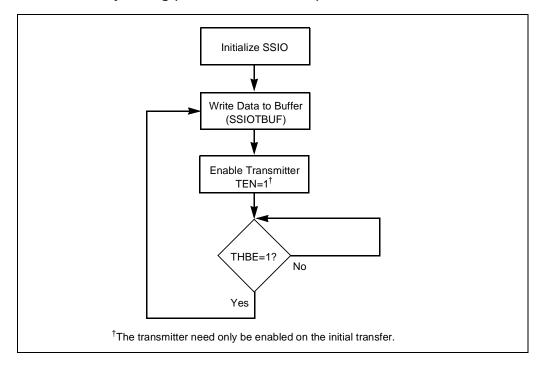

When the SSIO is transmitting data (master or slave mode) the transmitter is turned off by clearing the TEN bit of the SSIOCON1 register. One way of indicating to the software to clear this bit is by waiting for the Transmit Holding Buffer Empty (THBE) signal to go active, indicating that the word written to the holding register is ready for transmission from the shift register. Even if the software waits for this signal and then writes to SSIOCON1 to disable TEN, depending on when TEN is cleared, the last word transmit may or may not take place.

If the TXCLK is significantly slower than the CPUCLK, it is possible for the THBE bit to be set and the TEN bit to be cleared all during the low time of the TXCLK (see diagram). In this case, even though the last word to be transmitted has been loaded into the shift register, it will not be shifted out.

Implication:

This errata applies to all applications that require non-continuous low speed synchronous serial transfers.

Workaround:

In order to assure that the last word is transmitted, the TEN bit must not be cleared until after the TXCLK transitions from low to high when the 1st bit of the last word is being transmitted. Consequently, the way to assure that this happens is to either: 1) utilize a timer to assure that enough time elapses from when the THBE bit goes high until the TXCLK goes high, or 2) execute a fixed number of NOPs after THBE goes high before clearing TEN. In either case, the length of the delay is dependent upon the frequency of TXCLK and the CPUCLK.

Status:

Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected stepping(s).

### 25. Back-To-Back Writes To Interrupt Controller May Cause Failure In Second Write

Problem:

When back-to-back write I/O operations are performed to the OCW2 register in either the master or the slave in the Interrupt Control Unit an error can occur in the second write operation. One flip-flop in the asynchronous logic of the ICU does not get set correctly. Back to back writes to the ICU are defined as two writes to the ICU without a read of the ICU in between them. It doesn't matter if there are other operations that occur between the writes.

When a data byte is written, bits 3 and 4 of the byte determine which internal register (OCW2, OCW3, or ICW1) is selected. The data bus retains the last value that was put on it. Because the flip-flop is in the wrong state for the second write, a race condition can occur if the data bus

changes too slowly with respect to the write signal inside the interrupt controller. It is possible for the old values of bits 3 and 4 to cause a short clock pulse to the wrong register before the new values of bits 3 and 4 are set.

The problem shows up most noticeably when the internal peripheral data bus has a value of XXX011XX on it from the last I/O operation and you write an end of interrupt command to OCW2. The data byte would be XXX00XXX and should select OCW2. Instead, the 01 that was on the bus temporarily selects OCW3 and latches a 1 into bit 2, setting the POLL bit. When the POLL bit is set, no further interrupt requests are passed from the interrupt controller to the CPU.

Implication:

This errata applies to all applications that use the interrupt control unit.

Workaround:

Doing a read operation at either the master or slave ICU after a write to that same address will always put the flip-flop to the correct value. The next write to the same address will then work correctly and not show the race condition. Note that register ICW1 is not affected by the flip-flop value, so the dummy read only needs to be done when writing to OCW2. See the sample end-of-interrupt code below:

```

MOV AL, eiodata

MOV DX, MPICPO ; Master ICU I/O address

OUT DX, AL

IN AL, DX ; Dummy read to set flip flop

```

Status:

Corrected on B stepping. Refer to Summary Table of Changes to determine the affected stepping(s).

### 26.

#### **DMA And Bus Arbiter Reset May Cause Bus Contention**

Problem:

The DMA and bus arbiter can be reset by writing to address 000DH (or F00DH) which is the DMACLR register. DMACLR is not actually a physical register, but rather the reset is caused by an address decode of an I/O write to this location. Even though this is the case, there can be local bus DMA data bus contention if the "data" written to DMACLR is not 00H. The result of this contention is that some of the DMA registers may not properly reset when DMACLR is written.

Implication:

This errata applies to all applications that use the DMA or bus arbiter.

Workaround:

Always write 00H to DMACLR when the DMA or bus arbiter needs to be reset. See sample code below.

```

MOV DX, 000DH ; DMACLR Address

MOV AL, 00H ; Must be 00H to avoid contention

OUT DX, AL ; Resets the DMA and Bus Arbiter

```

Status:

Corrected on B stepping. Refer to Summary Table of Changes to determine the affected stepping(s).

27. Internal HOLD Request Synchronization May Cause Data/Code Fetches To Be Corrupted

**Problem:** Any operation that asserts the internal hold request signal (iHOLD) may cause bus contention if

that request is removed before the iHLDA is returned valid. The requests that may cause this problem are DREQ0, DREQ1, HOLD, and the internal refresh request. The issue is that when the request is asserted the bus arbitration sequence starts in order to transfer control of the bus. If the request is pulled away at the wrong time, then the bus arbiter will continue to give the bus to the requester, but the core will recognize that the request has been removed and attempt to take control

of the bus also. This will result in contention on the bus and corrupted data/code.

**Implication:** This errata applies to all applications that use multiple bus masters.

Workaround: Make certain in the application that the DREQs or HOLD requests are not removed until either

DACK or HLDA respectively are returned by the processor. Note that for a two cycle DMA transfer only the requester cycle generates DACK, the target cycle doesn't. Consequently, the logic

must be able to ensure that DREQ is left active until the channel is serviced.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

28. Writing To One DMA Channel's Register When A Request From The Other

Channel Occurs May Cause An Improper Transfer.

**Problem:** If a DMA request occurs on one DMA channel while the processor is writing to the other channel's

registers (requester address, target address, or byte count) then it is possible for the transfer to be corrupted on the channel that made the request. The symptoms from this errata have occurred in two different ways under specific conditions. The first condition is if the transfer is a write (data transferred from requester to target), the requester is an 8-bit device and the target is a 16 bit device and the channel is programmed for two cycle, single transfer, single buffer mode. Under these conditions the last byte of the buffer is read from the requester but never written to the target. The second condition is the same as the first, except that the transfer is a read (data transferred from target to requester) instead of a write. In this condition there is one (or possibly more) too many

bytes written to the requester.

**Implication:** This errata applies to all applications that use both DMA channels and allow one to be enabled

while the other is being programmed.

**Workaround:** Do not attempt to reprogram one channel of the DMA while the other is enabled.

**Status:** No fix is planned. Refer to Summary Table of Changes to determine the affected stepping(s).

29. Insufficient Address Hold Time After WR# Goes High

**Problem:** The address hold time after WR# goes high does not meet the data sheet spec of 5 ns.

**Implication:** This errata applies to all applications that use the WR# signal as the write strobe to memory or I/O.

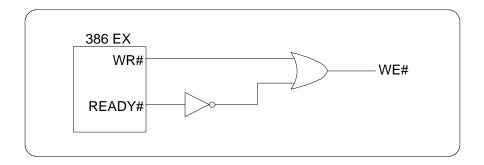

Workaround: The circuit shown below may be used to generate a write strobe if the READY# signal is not

generated too early in the T2 cycle. Please note this circuit has not been tested in a real design and is provided as an example only. For applications which cannot use the circuit below it is necessary to implement an external WE# signal using a simple state machine design. An example of what that state machine could look like is available in the EV386EX evaluation board design, or in the Point

of Sales Terminal reference design available from the WEB, BBS or through literature.

**Status:** Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected stepping(s).

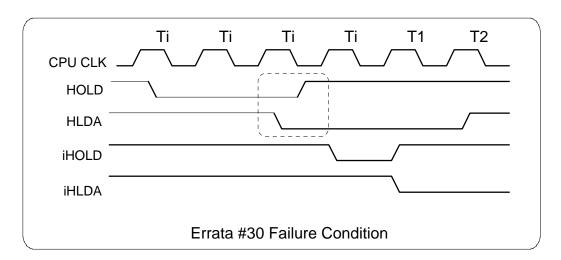

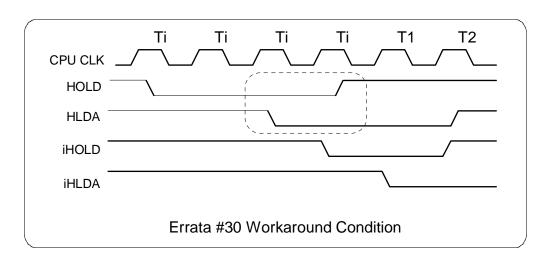

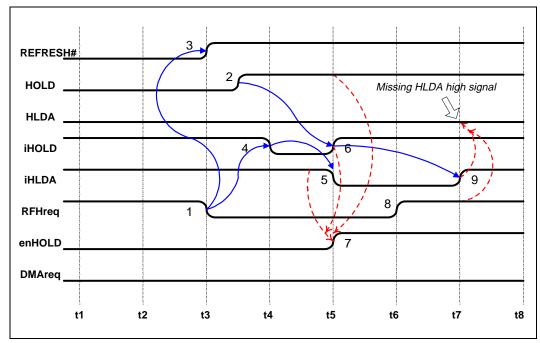

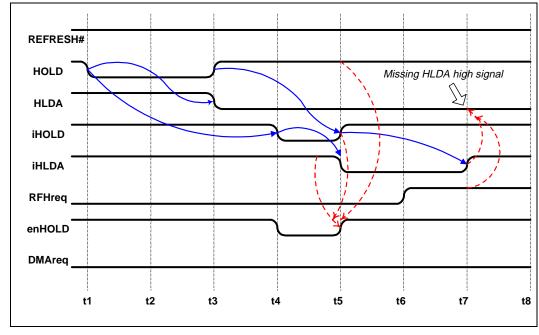

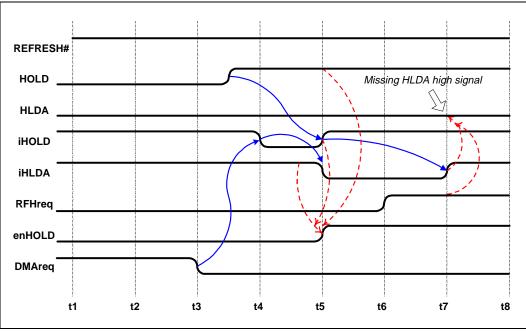

#### 30. HLDA Inactive To HOLD Active Arbitration Could Improperly Float The Bus

Problem:

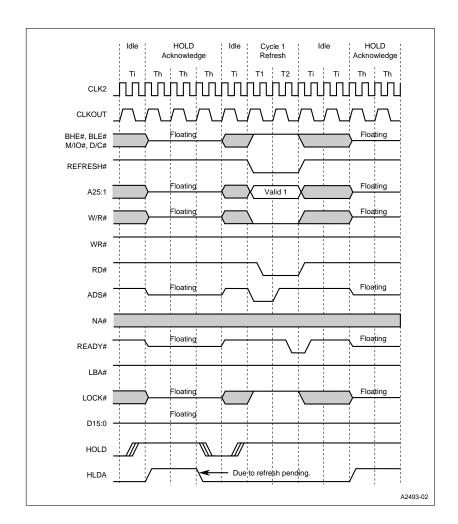

In a HOLD/HLDA cycle the HOLD signal must not be re-asserted until after HLDA is returned inactive. If, however, HOLD is asserted in the same T-state that HLDA goes inactive a problem may occur where the bus arbiter relinquishes control to the core and at the same time floats the bus by asserting the HLDA pin. The following waveform shows the conditions that cause this error. The signals iHOLD and iHLDA are internal signals and represent the HOLD input to the core and the HLDA output from the core (equivalent to the HOLD and HLDA signals on a Intel386<sup>TM</sup> SX processor). In this diagram a T1 occurs because a request was pending by the core during the previous HOLD cycle. One T-state after the arbiter releases the bus (HLDA = 0) it removes its iHOLD, and then the core removes iHLDA. As soon as the iHLDA is released, the T1 state starts. However, because of the timing of the next HOLD request, the bus arbiter re-asserts iHOLD and HLDA even though the core has not asserted iHLDA. The result is that the core continues to run its bus cycle and, at the same time, the bus arbiter has floated the external bus. It is also possible for the following to occur when HOLD/HLDA arbitration is at issue: HOLD is driven active during the T1 or Tw of a valid bus cycle. The processor begins the next bus cycle and generates HLDA. HLDA is active for only one T-state. ADS# is extended through the bus cycle. The alternate bus master sees the HLDA and performs its bus activity. HOLD is then driven inactive and the bus is returned to the Intel386<sup>TM</sup> EX Processor. At this point there is bus contention.

It is also possible for the following to occur when HOLD/HLDA arbitration is an issue: HOLD is driven active during the T1 or Tw of a valid bus cycle. The processor begins the next bus cycle and generates HLDA. HLDA is active for only one T-state. ADS# is extended through the bus cycle. The alternate bus master sees the HLDA and performs its bus activity. HOLD is then driven inactive and the bus is returned to the Intel386<sup>TM</sup> EX Processor. At this point there is bus contention.

**Implication:** This errata applies to all applications that use external bus masters with HOLD/HLDA arbitration.

**Workaround:** Synchronize the external HOLD request such that it is does not go active until at least one T-state after HLDA is inactive. See the following example waveform.

Another workaround is to delay the generation of HOLD until the last T2-state of a valid bus cycle (excluding refresh cycles or INTA cycles).

**Status:** Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 31. FLT# Does Not Float All Outputs

Asserting the FLT# pin does not float any of the I/O pins that have permanent weak pull-ups/pull-downs or I/O pins that have temporary weak pull-ups/pulldowns that are turned on. In these cases,

the actual pin drivers will be three-stated, but the pull-ups/pulldowns will force them to the given

state.

**Implication:** This errata is really only a problem when an In-Circuit-Emulator is being used. Many ICE systems

utilize a clamp on header that uses the FLT# pin to float the actual processor in order to "take over" the system. In this case, if a temporary pull-up/down has been turned off then asserting FLT# will float that pin. If, however, the target board is reset, the reset action takes priority over the FLT# and turns the temporary pull-up/down on again. If the application uses an external pull-up/down that pulls the pin to the opposite value as the internal pull-up/pull-down, the pin voltage will be

somewhere between 0V and Vcc.

**Workaround:** Make certain that external pull-ups/downs pull each pin to the same level as any internal pull-ups/

downs. See Appendix A table A-4 in the  $Intel386^{\mathrm{TM}}$  EX Embedded Microprocessor User's Manual

for a description of which pins have weak pull-ups/downs.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

Problem:

#### 32. SIO Break Could Be Missed

**Problem:** The SIO Break Interrupt in the LSR register indicates when a break condition has occurred. This

bit is cleared on reading the LSR. If the application is polling the line status register to detect a break interrupt it is possible for the read action to occur at the same time the SIO is setting the BI bit. If this occurs, the read action will prevent the BI bit from being set causing the program to miss the break. This occurs because the SIO uses different clock signals to set and clear the BI bit. Since these clock signals are not synchronous they could happen at the same time, and the clearing action

will take precedence.

**Implication:** This errata applies to any application that uses a polling routine to detect a break interrupt.

**Workaround:** A possible workaround is to send multiple breaks from the transmitting end of the SIO. In this case,

the SIO may miss the first, but detect the second.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

### 33. Arbitration Between Powerdown And Refresh Cycles May Leave Control Signals In Wrong State

**Problem:** Entering powerdown mode requires a HALT cycle to be executed after the powerdown bit in the

PWRCON register has been set. If a refresh request occurs at about the same time a condition may occur where the bus arbiter grants the bus to the RCU, and at the same time puts the device into powerdown mode. The symptom of this problem is that the ADS# and REFRESH# signals will

latch in their active states, and power consumption is higher than it should be.

**Implication:** This errata applies to any application that uses powerdown mode and the refresh control unit.

Workaround: Prior to executing the HALT instruction that puts the device into powerdown the RCU should be

disabled by clearing bit 15 of the RFSCON register. This refresh is not supported in powerdown

mode this should not create a problem.

Status: Corrected on C-stepping. Refer to Summary Table of Changes to determine the affected

stepping(s).

### 34. Refresh Control With More Than 2 Wait States Could Cause An Erroneous Bus Cycle

**Problem:** An arbitration fault occurs between the refresh control unit (RCU) and the bus interface unit (BIU)

under certain refresh conditions. If a refresh of DRAM occurs immediately following an I/O access of any type (this includes interrupts), an erroneous bus cycle may occur if the DRAM is configured for more than two wait states. This will cause the refresh cycle to be terminated after two wait

states and may cause corruption of data if the DRAM does require more than two wait states.

**Implication:** This errata impacts those applications using DRAM with more than 2 wait states and also utilizes

the internal Refresh Control Unit of the Intel386<sup>TM</sup> EX Processor.

Workaround: None. The only alternative at this point is to use DRAM that does not require more than two wait

states or to use an external DRAM controller.

Status: This errata applies to B1 stepping only. Refer to Summary Table of Changes to determine the

affected stepping(s).

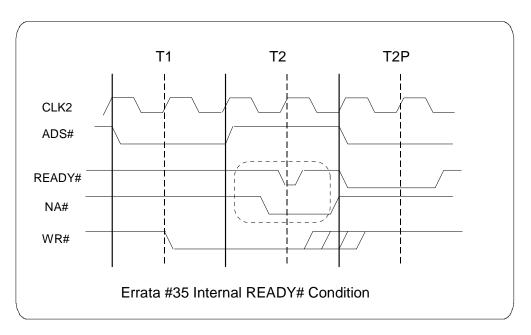

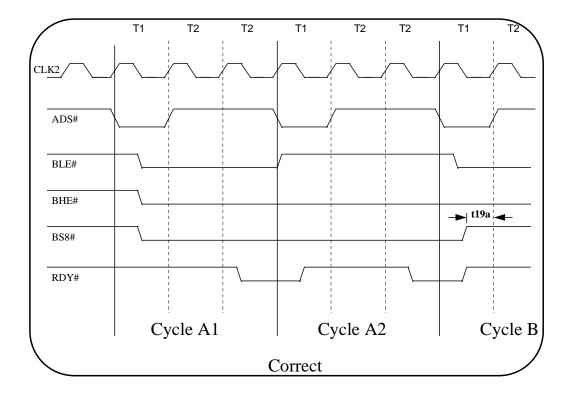

35. Internal READY# Generation Switching from Non-pipeline to Pipeline Can Be Temporarily Asserted

**Problem:** If the processor chip select is configured with zero wait states and is switching from non-pipeline