# **Cosmic Board for phyCORE-AM335x System on Module and Carrier Board**

# **Hardware Manual**

Product No SOM PCB No CB PCB No Edition : PCL-051/POB-002 : 1397.0 : 1396.1 : October 30, 2013

A product of a PHYTEC Technology Holding Company

In this manual are descriptions for copyrighted products that are not explicitly indicated as such. The absence of the trademark (TM) and copyright (©) symbols does not imply that a product is not protected. Additionally, registered patents and trademarks are similarly not explicitly indicated in this manual.

The information in this document has been carefully checked and is believed to be entirely reliable. However, PHYTEC Embedded Pvt. Ltd assumes no responsibility for any inaccuracies. PHYTEC Embedded Pvt. Ltd neither gives any guarantee nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product. PHYTEC Embedded Pvt. Ltd reserves the right to alter the information contained herein without prior notification and accepts no responsibility for any damages which might result.

Additionally, PHYTEC Embedded Pvt. Ltd offers no guarantee nor accepts any liability for damages arising from the improper usage or improper installation of the hardware or software. PHYTEC Embedded Pvt. Ltd further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

© Copyright 2013 PHYTEC Embedded Pvt. Ltd, Koramangala, Bangalore.

Rights - including those of translation, reprint, broadcast, photomechanical or similar reproduction and storage or processing in computer systems, in whole or in part - are reserved. No reproduction may occur without the express written consent from PHYTEC Embedded Pvt. Ltd

|                                                                                                                                                                  | INDIA                                | EUROPE                                                                                 | NORTH AMERICA                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Address: PHYTEC Embedded<br>Pvt. Ltd.<br>#16/9C,3rd Floor,3rd<br>Main,Opp.Police<br>Station<br>Koramangala,8 <sup>th</sup> block<br>, Bangalore -560095<br>India |                                      | PHYTEC<br>Technologie Holding<br>AG<br>Robert-Koch-Str. 39<br>D-55129 Mainz<br>GERMANY | PHYTEC America LLC<br>203 Parfitt Way SW,<br>Suite G100<br>Bainbridge Island, WA<br>98110<br>USA |

|                                                                                                                                                                  | +91-80-40867046<br>sales@phytec.in   | +49 (800) 0749832<br>sales@phytec.de                                                   | 1 (800) 278-9913<br>sales@phytec.com                                                             |

| Technical Support:                                                                                                                                               | +91-80-40867047<br>support@phytec.in | +49 (6131) 9221-31<br>support@phytec.de                                                | 1 (800) 278-9913<br>support@phytec.com                                                           |

| Fax:                                                                                                                                                             | -                                    | +49 (6131) 9221-33                                                                     | 1 (206) 780-9135                                                                                 |

| Website:                                                                                                                                                         | http://www.phytec.in                 | http://www.phytec.eu<br>http://www.phytec.de                                           | http://www.phytec.com                                                                            |

| Table of Contents                                                      |    |

|------------------------------------------------------------------------|----|

| LIST OF TABLES                                                         | 4  |

| LIST OF FIGURES                                                        | 5  |

| CONVENTIONS, ABBREVIATIONS, AND ACRONYMS                               | 6  |

| 1 INTRODUCTION                                                         | 10 |

| 1.1 Cosmic Board Features<br>1.2 Block Diagram                         |    |

| 2 PCL-051/PHYCORE-AM335X SYSTEM ON MODULE                              | 12 |

| 2.1 PHYCORE-AM335x Features                                            | 13 |

| 3 POWER                                                                | 14 |

| 3.1 JUMPER SETTINGS (JP1)<br>3.2 USB Power (X6)<br>3.3 Wall Power (X2) | 14 |

| 4 ETHERNET (X3)                                                        | 16 |

| 5 RS-232 CONSOLE (X8)                                                  | 17 |

| 6 USB CONNECTIVITY                                                     | 18 |

| 6.1 USB Ноsт (X3)<br>6.2 USB ОТG (X6)                                  |    |

| 7 SD CARD (X18)                                                        |    |

| 7.1 Inserting and Removing an SD Card                                  |    |

| 8 HDMI (X16)                                                           | 20 |

| 9 USER BUTTONS                                                         | 21 |

| 10 SYSTEM RESET BUTTON (S5)                                            | 22 |

| 11 USER LEDS                                                           | 23 |

| 12 BOOT SELECTION (JP5)                                                | 24 |

| 13 REAL-TIME CLOCK OPTIONS (RTC)                                       | 25 |

| 13.1 PMIC RTC                                                          |    |

| 14 CONTROLLER AREA NETWORK (CAN) INTERFACES                            | 26 |

| 15 EXPANSION CONNECTORS (X19, X20)                                     | 27 |

| 16 TECHNICAL SPECIFICATIONS                                            | 35 |

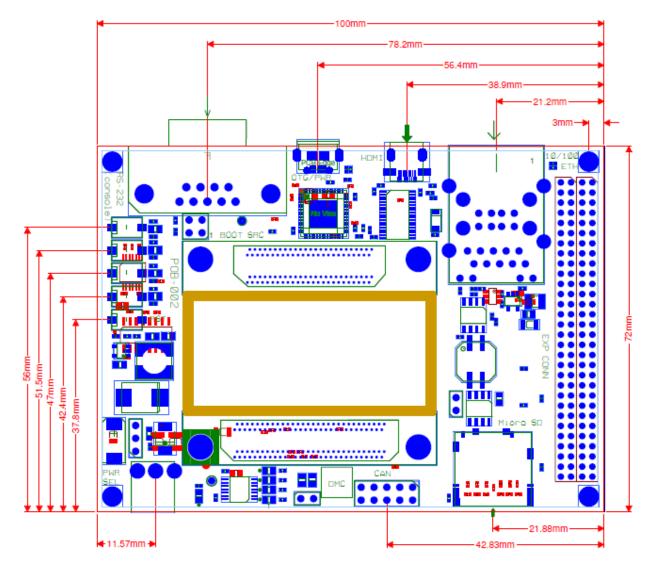

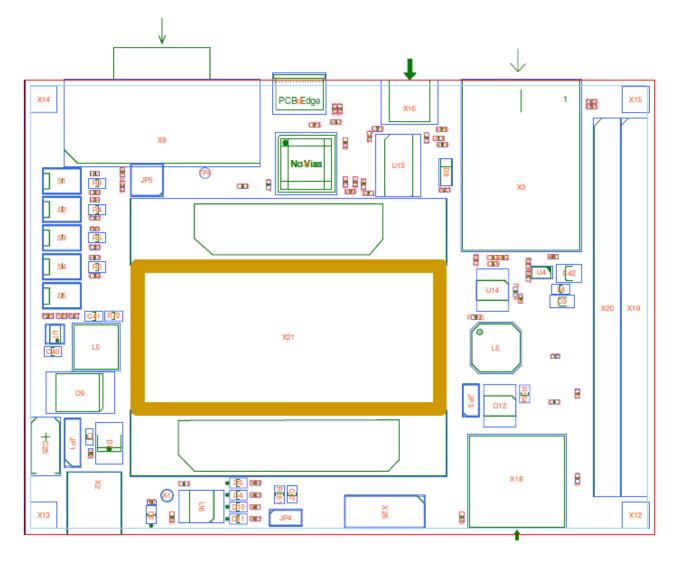

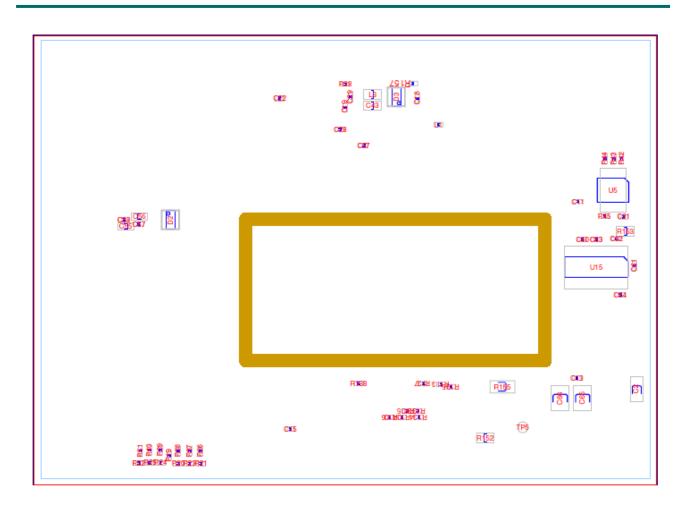

| 17 COMPONENT PLACEMENT DIAGRAMS                                        | 37 |

| REVISION HISTORY                                                       | 39 |

## List of Tables

| TABLE I- 2. TYPES OF SIGNALS7TABLE 3- 1. JUMPER SETTINGS (JP1)14TABLE 5- 1. CONNECTOR X8 PIN DESCRIPTIONS17TABLE 12- 1. JUMPER SETTINGS AND DESCRIPTIONS24TABLE 12- 1. JUMPER SETTINGS AND DESCRIPTIONS26TABLE 14- 1. CONNECTOR X25 PIN DESCRIPTIONS26TABLE 15- 2. POWER SIGNAL MAP27TABLE 15- 3. SYSTEM SIGNAL MAP27TABLE 15- 4. JTAG SIGNAL MAP27TABLE 15- 5. CAN SIGNAL MAP28TABLE 15- 6. I2C SIGNAL MAP28TABLE 15- 7. UART SIGNAL MAP28TABLE 15- 8. SPI SIGNAL MAP29TABLE 15- 9. ADC SIGNAL MAP29TABLE 15- 10. NAND (GPMC) SIGNAL MAP30TABLE 15- 11. LCD SIGNAL MAP30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP34TABLE 16- 1. TECHNICAL SPECIFICATIONS36TABLE 16- 1. TECHNICAL SPECIFICATIONS36TABLE 18- 10. RAPUSION HISTORY39 | TABLE I- 1. ABBREVIATIONS AND ACRONYMS USED IN THIS MANUAL      | 6  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----|

| TABLE 5- 1. CONNECTOR X8 PIN DESCRIPTIONS17TABLE 12- 1. JUMPER SETTINGS AND DESCRIPTIONS24TABLE 14- 1. CONNECTOR X25 PIN DESCRIPTIONS26TABLE 15- 2. POWER SIGNAL MAP27TABLE 15- 3. SYSTEM SIGNAL MAP27TABLE 15- 4. JTAG SIGNAL MAP27TABLE 15- 5. CAN SIGNAL MAP27TABLE 15- 6. I2C SIGNAL MAP28TABLE 15- 7. UART SIGNAL MAP28TABLE 15- 8. SPI SIGNAL MAP28TABLE 15- 9. ADC SIGNAL MAP29TABLE 15- 10. NAND (GPMC) SIGNAL MAP30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP34TABLE 16- 1. TECHNICAL SPECIFICATIONS36                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 |    |

| TABLE 5- 1. CONNECTOR X8 PIN DESCRIPTIONS17TABLE 12- 1. JUMPER SETTINGS AND DESCRIPTIONS24TABLE 14- 1. CONNECTOR X25 PIN DESCRIPTIONS26TABLE 15- 2. POWER SIGNAL MAP27TABLE 15- 3. SYSTEM SIGNAL MAP27TABLE 15- 4. JTAG SIGNAL MAP27TABLE 15- 5. CAN SIGNAL MAP27TABLE 15- 6. I2C SIGNAL MAP28TABLE 15- 7. UART SIGNAL MAP28TABLE 15- 8. SPI SIGNAL MAP28TABLE 15- 9. ADC SIGNAL MAP29TABLE 15- 10. NAND (GPMC) SIGNAL MAP30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP34TABLE 16- 1. TECHNICAL SPECIFICATIONS36                                                                                                                                                                                                                                                                                                                                                                                                 | TABLE 3-1. JUMPER SETTINGS (JP1)                                | 14 |

| TABLE 14- 1. CONNECTOR X25 PIN DESCRIPTIONS.26TABLE 15- 2. POWER SIGNAL MAP.27TABLE 15- 3. SYSTEM SIGNAL MAP.27TABLE 15- 4. JTAG SIGNAL MAP.27TABLE 15- 5. CAN SIGNAL MAP.28TABLE 15- 6. I2C SIGNAL MAP.28TABLE 15- 7. UART SIGNAL MAP.28TABLE 15- 8. SPI SIGNAL MAP.29TABLE 15- 9. ADC SIGNAL MAP.29TABLE 15- 10. NAND (GPMC) SIGNAL MAP.30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP.31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP.32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP.34TABLE 16- 1. TECHNICAL SPECIFICATIONS36                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TABLE 5-1. CONNECTOR X8 PIN DESCRIPTIONS                        | 17 |

| TABLE 15- 2. POWER SIGNAL MAP.       27         TABLE 15- 3. SYSTEM SIGNAL MAP.       27         TABLE 15- 4. JTAG SIGNAL MAP.       27         TABLE 15- 5. CAN SIGNAL MAP.       28         TABLE 15- 6. I2C SIGNAL MAP.       28         TABLE 15- 7. UART SIGNAL MAP.       28         TABLE 15- 7. UART SIGNAL MAP.       28         TABLE 15- 8. SPI SIGNAL MAP.       28         TABLE 15- 9. ADC SIGNAL MAP.       29         TABLE 15- 9. ADC SIGNAL MAP.       29         TABLE 15- 10. NAND (GPMC) SIGNAL MAP.       29         TABLE 15- 10. NAND (GPMC) SIGNAL MAP.       30         TABLE 15- 11. LCD SIGNAL MAP.       30         TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP.       31         TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP.       32         TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP.       34         TABLE 16- 1. TECHNICAL SPECIFICATIONS       36                                                                                                                  |                                                                 |    |

| TABLE 15-3. SYSTEM SIGNAL MAP.       27         TABLE 15-4. JTAG SIGNAL MAP.       27         TABLE 15-5. CAN SIGNAL MAP.       28         TABLE 15-6. I2C SIGNAL MAP.       28         TABLE 15-7. UART SIGNAL MAP.       29         TABLE 15-9. ADC SIGNAL MAP.       29         TABLE 15-9. ADC SIGNAL MAP.       29         TABLE 15-10. NAND (GPMC) SIGNAL MAP.       30         TABLE 15-11. LCD SIGNAL MAP.       30         TABLE 15-12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP.       31         TABLE 15-13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP.       32         TABLE 15-14. ETHERNET (RGMII) SIGNAL MAP.       34         TABLE 16-1. TECHNICAL SPECIFICATIONS       36                                                                                                                                                                                         | TABLE 14-1. CONNECTOR X25 PIN DESCRIPTIONS.                     | 26 |

| TABLE 15- 4. JTAG SIGNAL MAP       27         TABLE 15- 5. CAN SIGNAL MAP       28         TABLE 15- 6. I2C SIGNAL MAP       28         TABLE 15- 7. UART SIGNAL MAP       28         TABLE 15- 7. UART SIGNAL MAP       28         TABLE 15- 8. SPI SIGNAL MAP       29         TABLE 15- 9. ADC SIGNAL MAP       29         TABLE 15- 10. NAND (GPMC) SIGNAL MAP       30         TABLE 15- 11. LCD SIGNAL MAP       30         TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP       31         TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP       32         TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP       34         TABLE 16- 1. TECHNICAL SPECIFICATIONS       36                                                                                                                                                                                                                                                                                                                                    |                                                                 |    |

| TABLE 15- 5. CAN SIGNAL MAP.28TABLE 15- 6. I2C SIGNAL MAP.28TABLE 15- 7. UART SIGNAL MAP.28TABLE 15- 8. SPI SIGNAL MAP.29TABLE 15- 9. ADC SIGNAL MAP.29TABLE 15- 10. NAND (GPMC) SIGNAL MAP.30TABLE 15- 11. LCD SIGNAL MAP.30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP.31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP.32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP.34TABLE 16- 1. TECHNICAL SPECIFICATIONS36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TABLE 15-3. SYSTEM SIGNAL MAP                                   | 27 |

| TABLE 15- 6. I2C SIGNAL MAP28TABLE 15- 7. UART SIGNAL MAP28TABLE 15- 8. SPI SIGNAL MAP29TABLE 15- 9. ADC SIGNAL MAP29TABLE 15- 10. NAND (GPMC) SIGNAL MAP30TABLE 15- 11. LCD SIGNAL MAP30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP34TABLE 16- 1. TECHNICAL SPECIFICATIONS36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                 |    |

| TABLE 15- 7. UART SIGNAL MAP28TABLE 15- 8. SPI SIGNAL MAP29TABLE 15- 9. ADC SIGNAL MAP29TABLE 15- 10. NAND (GPMC) SIGNAL MAP30TABLE 15- 11. LCD SIGNAL MAP30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP34TABLE 16- 1. TECHNICAL SPECIFICATIONS36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 |    |

| TABLE 15- 8. SPI SIGNAL MAP.29TABLE 15- 9. ADC SIGNAL MAP.29TABLE 15- 10. NAND (GPMC) SIGNAL MAP.30TABLE 15- 11. LCD SIGNAL MAP.30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP.31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP.32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP.34TABLE 16- 1. TECHNICAL SPECIFICATIONS36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TABLE 15- 6. I2C SIGNAL MAP                                     | 28 |

| TABLE 15- 9. ADC SIGNAL MAP.29TABLE 15- 10. NAND (GPMC) SIGNAL MAP.30TABLE 15- 11. LCD SIGNAL MAP.30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP.31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP.32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP.34TABLE 16- 1. TECHNICAL SPECIFICATIONS36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TABLE 15-7. UART SIGNAL MAP                                     | 28 |

| TABLE 15- 10. NAND (GPMC) SIGNAL MAP30TABLE 15- 11. LCD SIGNAL MAP30TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP31TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP32TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP34TABLE 16- 1. TECHNICAL SPECIFICATIONS36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TABLE 15-8. SPI SIGNAL MAP                                      | 29 |

| TABLE 15- 11. LCD SIGNAL MAP       30         TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP       31         TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP       32         TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP       34         TABLE 16- 1. TECHNICAL SPECIFICATIONS       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |    |

| TABLE 15- 12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP       31         TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP       32         TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP       34         TABLE 16- 1. TECHNICAL SPECIFICATIONS       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TABLE 15- 10. NAND (GPMC) SIGNAL MAP                            |    |

| TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP.       32         TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP       34         TABLE 16- 1. TECHNICAL SPECIFICATIONS       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                 |    |

| TABLE 15- 13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP.       32         TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP       34         TABLE 16- 1. TECHNICAL SPECIFICATIONS       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TABLE 15-12. MULTICHANNEL AUDIO SERIAL PORTS (MCASP) SIGNAL MAP | 31 |

| TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP         34           TABLE 16- 1. TECHNICAL SPECIFICATIONS         36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TABLE 15-13. GENERAL PURPOSE I/O'S (GPIO'S) SIGNAL MAP          | 32 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TABLE 15- 14. ETHERNET (RGMII) SIGNAL MAP                       | 34 |

| TABLE 18- 1. REVISION HISTORY   39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TABLE 18-1. REVISION HISTORY                                    | 39 |

## List of Figures

| FIGURE 1-1. COSMIC BOARD                      |  |

|-----------------------------------------------|--|

| FIGURE 1- 2. COSMIC BOARD BLOCK DIAGRAM       |  |

| FIGURE 5-1. RS-232 CONNECTOR X8 PIN NUMBERING |  |

| FIGURE 12-1. JUMPER NUMBERING SCHEME.         |  |

| FIGURE 17-1. COSMIC BOARD TOP                 |  |

| FIGURE 17-2. COSMIC BOARD BOTTOM              |  |

## **Conventions, Abbreviations, and Acronyms**

#### Conventions

The conventions used in this manual are as follows:

- Signals that are preceded by a "/" character are designated as active low signals. Their active state is when they are driven low, or are driving low; for example : /RESET.

- Tables show the default setting or jumper position in **bold**, **teal** text.

- Text in blue indicates a hyperlink, either internal or external to the document. Click these links to quickly jump to the applicable URL, part, chapter, table, or figure.

- References made to the phyCORE-Connector always refer to the high density Samtec connectors on the underside of the Cosmic Board System on Module.

#### **Abbreviations and Acronyms**

Many acronyms and abbreviations are used throughout this manual. Use the table below to navigate unfamiliar terms used in this document.

| Abbreviation | Definition                                                                                                                                                             |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BSP          | Board Support Package (Software delivered with the Development Kit including an operating system (Windows or Linux) preinstalled on the module and Development Tools). |  |  |  |

| СВ           | Carrier Board; used in reference to the PCM-953/Cosmic Board Carrier<br>Board                                                                                          |  |  |  |

| DFF          | D flip-flop                                                                                                                                                            |  |  |  |

| EMB          | External memory bus                                                                                                                                                    |  |  |  |

| EMI          | Electromagnetic Interference                                                                                                                                           |  |  |  |

| GPI          | General purpose input                                                                                                                                                  |  |  |  |

| GPIO         | General purpose input and output                                                                                                                                       |  |  |  |

| GPO          | General purpose output                                                                                                                                                 |  |  |  |

| IRAM         | Internal RAM; the internal static RAM on the TI AM335x processor                                                                                                       |  |  |  |

| J            | Solder jumper; these types of jumpers require solder equipment to remove and place                                                                                     |  |  |  |

| JP           | Solderless jumper; these types of jumpers can be removed and placed by hand with no special tools                                                                      |  |  |  |

| PCB          | Printed circuit board                                                                                                                                                  |  |  |  |

| PDI          | PHYTEC Display Interface; defined to connect PHYTEC display adapter boards or custom adapters                                                                          |  |  |  |

| PEB          | PHYTEC Extension Board                                                                                                                                                 |  |  |  |

| PMIC         | Power Management Integrated Circuit                                                                                                                                    |  |  |  |

| PoE          | Power over Ethernet                                                                                                                                                    |  |  |  |

| PoP          | Package on Package                                                                                                                                                     |  |  |  |

#### Table i- 1. Abbreviations and Acronyms Used in This Manual

| PoR | Power-on reset           |  |

|-----|--------------------------|--|

| RTC | Real-time clock          |  |

| SMT | Surface mount technology |  |

## Table i-1. Abbreviations and Acronyms Used in This Manual

| Abbreviation | Definition                                                                                                          |  |

|--------------|---------------------------------------------------------------------------------------------------------------------|--|

| SOM          | System on Module; used in reference to the PCM-051/Cosmic Board System on Module                                    |  |

| Sx           | User button Sx (S1, S2, etc.) used in reference to the available user buttons, or DIP switches on the Carrier Board |  |

| TRM          | Technical Reference Manual                                                                                          |  |

| VBAT         | SOM battery supply input                                                                                            |  |

Different types of signals are brought out at the phyCORE-Connector. The following table lists the abbreviations used to specify the type of a signal.

| Type of Signal              | Description                                              | Abbreviation |

|-----------------------------|----------------------------------------------------------|--------------|

| Power                       | Supply voltage                                           | PWR          |

| Ref-Voltage                 | Reference voltage                                        | REF          |

| USB-Power                   | USB voltage                                              | USB          |

| Input                       | Digital input                                            | IN           |

| Output                      | Digital output                                           | OUT          |

| Input with pull-up          | Input with pull-up (jumper or open-<br>collector output) | IPU          |

| Input/output                | Bidirectional input/output                               | IO           |

| 5V Input with pull-<br>down | 5V tolerant input with pull-down                         | 5V_PD        |

| LVDS                        | Differential line pairs 100 Ohm LVDS level               | LVDS         |

| Differential 90 Ohm         | Differential line pairs 90 Ohm                           | DIFF90       |

| Differential 100 Ohm        | Differential line pairs 100 Ohm                          | DIFF100      |

| Analog                      | Analog input or output                                   | Analog       |

| Preface                     |                                                          |              |

## Table i- 2. Types of Signals

## Pretace

This Cosmic Board Hardware Manual describes the System on Module's design and

functions. Precise specifications for the TI AM335x processor can be found in the processor datasheet and/or user's manual.

In this hardware manual and in the schematics, active low signals are denoted by a "/" preceding the signal name, for example: /RD. A "0" represents a logic-zero or low-level signal, while a "1" represents a logic one or high-level signal.

#### Declaration of Electro Magnetic Conformity of the PHYTEC Cosmic Board

PHYTEC System on Modules (SOMs) are designed for installation in electrical appliances or, combined with the PHYTEC Carrier Board, can be used as dedicated Evaluation Boards (for use as a test and prototype platform for hardware/software development) in laboratory environments.

#### CAUTION:

PHYTEC products lacking protective enclosures are subject to damage by ESD and, hence, may only be unpacked, handled or operated in environments in which sufficient precautionary measures have been taken in respect to ESD-dangers. It is also necessary that only appropriately trained personnel (such as electricians, technicians and engineers) handle and/or operate these products. Moreover, PHYTEC products should not be operated without protection circuitry if connections to the product's pin header rows are longer than 3 m.

PHYTEC products fulfill the norms of the European Union's Directive for Electro Magnetic Conformity only in accordance to the descriptions and rules of usage indicated in this hardware manual (particularly in respect to the pin header row connectors, power connector and serial interface to a host-PC).

Implementation of PHYTEC products into target devices, as well as user modifications and extensions of PHYTEC products, is subject to renewed establishment of conformity to, and certification of, Electro Magnetic Directives. Users should ensure conformance following any modifications to the products as well as implementation of the products into target systems.

The Cosmic Board is one of a series of PHYTEC System on Modules that can be populated with different controllers and, hence, offers various functions and configurations. PHYTEC supports a variety of 8/16 and 32-bit controllers in two ways:

- 1. As the basis for Rapid Development Kits which serve as a reference and Evaluation platform.

- 2. As insert-ready, fully functional phyCORE OEM modules, which can be Embedded directly into the user's peripheral hardware design.

Implementation of an OEM-able SOM subassembly as the "core" of your embedded design allows you to focus on hardware peripherals and firmware without expending resources to "re-invent" microcontroller circuitry. Furthermore, much of the value of the

phyCORE module lies in its layout and test.

Production-ready Board Support Packages (BSPs) and Design Services for our hardware further reduce development time and expenses. Take advantage of PHYTEC products to shorten time-to-market, reduce development costs, and avoid substantial design issues and risks. For more information go to:

http://www.phytec.in/services/hardware.html

#### Product Change Management

In addition to our HW and SW offerings, the buyer will receive a free obsolescence maintenance service for the HW provided when purchasing a PHYTEC SOM.

Our Product Change Management Team of developers is continuously processing all incoming PCN's (Product Change Notifications) from vendors and distributors concerning parts which are being used in our products. Possible impacts to the functionality of our products, due to changes of functionality or obsolesce of a certain part, are evaluated in order to take the right measures in purchasing or within our HW/SW design.

Our general philosophy here is: We never discontinue a product as long as there is demand for it.

Therefore a set of methods has been established to fulfill our philosophy:

#### **Avoidance strategies**

- Avoid changes by evaluating longevity of a part during design-in phase.

- Ensure availability of equivalent second source parts.

- Maintain close contact with part vendors for awareness of roadmap strategies.

#### Change management in case of functional changes

• Avoid impacts on Product functionality by choosing equivalent replacement parts.

• Avoid impacts on Product functionality by compensating changes through HW redesign or backward compatibility

#### SW maintenance

• Provide early change notifications concerning functional relevant changes of our Products.

#### Change management in rare event of an obsolete and non replaceable part

- Ensure long term availability by stocking parts through last time buy management, according to product forecasts.

- Offer long term frame contract to customers.

We refrain from providing detailed, part-specific information within this manual, which is subject to changes, due to ongoing part maintenance for our products.

## **1** Introduction

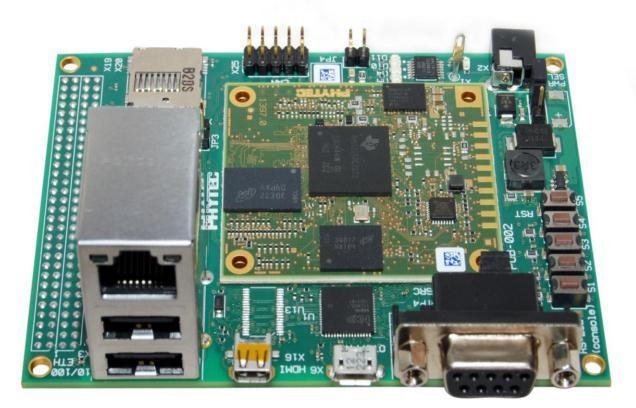

Figure 1- 1. Cosmic Board

The Cosmic Board for phyCORE-AM335x is a low-cost, feature-rich software development platform supporting the TI AM335x processor families. At the core of the Cosmic board is the PCL-051/phyCORE-AM335x System On Module (SOM) in a direct solder form factor, containing the AM335x processor, SDRAM, NAND Flash, power regulation, supervision, transceivers, and other core functions required to support the Cosmic AM335x Board. Surrounding the SOM is the POB-002/Cosmic Carrier Board, adding power input, buttons, connectors, signal breakout, and HDMI connectivity amongst other things.

The PCL-051 System On Module is a connector-less, BGA style variant of the PCM-051/phyCORE-AM335x SOM. Unlike traditional PHYTEC SOM products that support high density connectors, the PCL-051 SOM is directly soldered down to its Carrier Board using PHYTEC's Direct Solder Connect technology. This solution offers an ultra-low cost Single Board Computer for the AM335x processor, while maintaining most of the advantages of the SOM concept.

Adding the phyCORE-AM335x SOM into your own design is as simple as ordering the connectored version (PCM-051) and making use of our Cosmic Carrier Board (POB-002), or RDK Carrier Board (PCM-953) reference schematics. A summary of the Cosmic Board features, along with a block diagram are presented below.

## **1.1 Cosmic Board Features**

- phyCORE-AM335x System On Module

- Board power over:

- USB OTG Connector

- Wall Adapter Input

- High Speed USB Host Connector (standard A)

- High Speed USB OTG Connector (micro AB)

- 10/100 Ethernet RJ-45 Jack

- Micro SD Card Slot

- Micro HDMI connector supporting 640x480 @ 24bpp

- RS-232 Console Connectivity via DB-9

- Boot Selection Jumpers (NAND or SD Card or NOR)

- 4x User Buttons

- 4x User LEDs

- 120-pin, 2mm header socket for easy access to AM335x processor signals

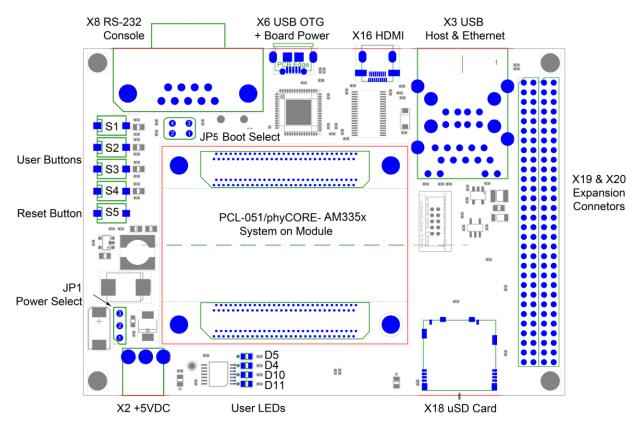

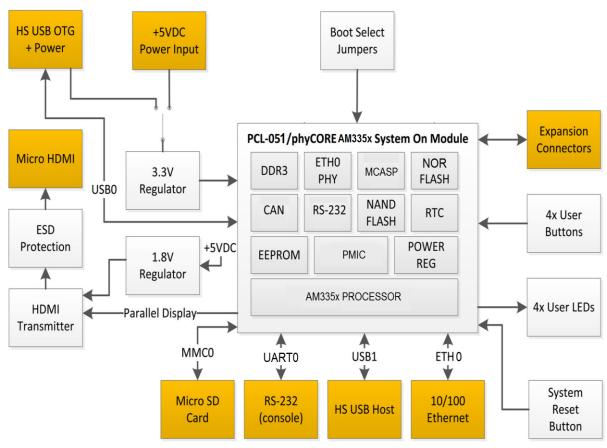

## 1.2 Block Diagram

POB-002/Cosmic Carrier Board

## 2 PCL-051/phyCORE-AM335x System on Module

This chapter gives a brief introduction to the PCL-051/phyCORE-AM335x System on Module (SOM), highlighting its benefits and features. For more detailed information, please refer to the Hardware Manual for the modular, connectored version of the SOM (PCM-051) by <u>clicking here</u>.

The phyCORE-AM335x belongs to PHYTEC's phyCORE System on Module (SOM) family. The phyCORE SOMs represent the continuous development of PHYTEC SOM technology. Like its mini-, micro-, and nanoMODUL predecessors, the phyCORE boards integrate all core elements of a microcontroller system on a subminiature board and are designed in a manner that ensures their easy expansion and embedding in peripheral hardware developments.

As independent research indicates that approximately 70% of all EMI (Electro Magnetic Interference) problems stem from insufficient supply voltage grounding of electronic components in high frequency environments, the phyCORE board design features an increased pin package. The increased pin package allows dedication of approximately 20% of all connector pins on the phyCORE boards to ground. This improves EMI and EMC characteristics and makes it easier to design complex applications meeting EMI and EMC guidelines using phyCORE boards even in high noise environments.

phyCORE boards achieve their small size through modern SMD technology and multilayer design. In accordance with the complexity of the module, 0402-packaged SMD components and laser-drilled Microvias are used on the boards, providing phyCORE users with access to this cutting edge miniaturization technology for integration into their own design.

The PCM-051, connectored version of the phyCORE-AM335x is a sub-miniature (41 x 51 mm) insert-ready SOM populated with AM335x processor. Its universal design enables its insertion into a wide range of embedded applications. All processor signals and ports extend from the processor to high-density pitch (0.5 mm) connectors aligning two sides of the board. This allows the SOM to be plugged like a "big chip" into a target application.

The PCL-051, connectorless version of the phyCORE-AM335x populating the Cosmic Board is identical to the connectored version, with the exception of the connection interface. Instead of two high density connectors aligning the edges of the board, the PCL-051 solders directly down to its Carrier Board with a BGA style footprint.

Precise specifications for the processor populating the board can be found in the applicable processor user's manual and datasheet. The descriptions in this manual are based on the AM335x processor. No description of compatible processor derivative functions is included, as such functions are not relevant for the basic functioning of the Cosmic Board.

## 2.1 phyCORE-AM335x Features

- Insert-ready, sub-miniature (41 mm x 51 mm) System on Module (SOM) subassembly in low EMI design, achieved through advanced SMD technology

- Populated with the TI AM335x (Cortex-A8) processor

- Max. 720 MHz core clock frequency

- Boot from NAND Flash or SPI Flash

- Controller signals and ports extend to two BGA-style connection interfaces aligning two sides of the board, enabling it to be soldered directly into the target application

- Single supply voltage of 3.3 V (max.1 A)

- All controller required supplies generated on board

- Improved interference safety achieved through multi-layer PCB technology and dedicated ground pins

- 512 MB (up to 1 GB) on-board NAND Flash

- 512 MB DDR3 SDRAM

- 4 kB (up to 32 kB) I2C EEPROM

- 8 MB SPI Flash

- One RS-232 two-signal (Tx/Rx) serial interfaces, or one RS-232 interface with hardware flow control, configured through software

- Six UARTs

- Dual USB OTG 2.0 High-Speed Controller with PHY

- Two 10/100/1000 MBit Ethernet interfaces with internal L2-Switch and IEEE1588 PTP for Realtime Ethernet (available as RMII TTL signals or 10/100 differential pairs)

- Three I2C interfaces with SMBUS support

- Two Serial Peripheral Interfaces (SPI)

- Two CAN interfaces with transceivers

- Display interface with 24 data bits

- Multichannel Audio Serial Ports

- One 8-channel, analog to digital (ADC) inputs

- JTAG

- 4-bit Secure Digital Host interface (SD/MMC)

- Real-Time Clock

- -40 to 85 degree Celcius operating temperature range

#### 3 Power

Power is supplied to the system using two methods:

- 1. USB power via connector X6

- 2. Wall power via connector X2

USB power provides an easy, single-cable solution for both power and console connectivity. System functionality is limited when powering the board off of USB. Most features of the board will function under USB power, with the exception of USB host and any add-on boards connected via the Expansion Connectors. Select the power option by configuring jumper JP1 using Table 3-1 below.

#### 3.1 Jumper Settings (JP1)

#### Table 3-1. Jumper Settings (JP1)

| Jumper<br>Position | Description |  |

|--------------------|-------------|--|

| 1+2                | Wall Power  |  |

| 2+3                | USB Power   |  |

See <u>Figure 1-1</u> for the location of jumper JP1. Pin 1 is marked on the PCB with a clipped corner on the component outline silk screen.

#### 3.2 USB Power (X6)

USB power can be used if the USB host interface is not required, nor any add-on boards connected to the Expansion Connectors (X19, X20) are required.

Use a standard USB-A to micro-AB, or micro-B connected to a PC to power the board and provide console access. A wall-outlet charger can be used to power the board but will eliminate the use of serial over USB.

Configure the board for USB power by setting JP1 to 2+3. See <u>Figure 1-1</u> for the location of jumper JP1.

#### 3.3 Wall Power (X2)

Wall power should be used when USB host, or expansion connector add-on boards are used. Both scenarios draw additional power not available through the USB OTG connector at X6.

A suitable +5VDC +- 5% / 1A or greater wall power adapter should be used with a center

positive contact. An appropriate power supply can be ordered with the kit at the time you place your order. Configure the board for wall power by setting JP1 to 1+2. See Figure 1-1 for the location of jumper JP1.

## CAUTION:

Do not use a laboratory adapter to supply power to the Carrier Board! Power spikes during power-on could destroy the phyCORE module mounted on the Carrier Board. Do not change jumper settings while the Carrier Board is supplied with power.

## 4 Ethernet (X3)

The 10/100 ETH0 interface, derived from the TI AM335x processor RMII1 signals, is accessible at an RJ-45 connector at X3 (USB Dual Standard A and Ethernet).

LEDs are integrated on the connector for indication of LINK (green) and SPEED (yellow).

The Ethernet PHY on the SOM supports the HP Auto-MDIX function, eliminating the need for considerations of a direct connect LAN cable or cross-over patch cable. The transceivers detect the TX and RX signals of the connected devices and automatically configure their RX and TX pins accordingly.

## 5 RS-232 Console (X8)

The DB9 connector X8 provides connectivity to the Cosmic (UART) signals at RS-232 level. This interface does not include the Cosmic's UART0\_RTS and UART0\_CTS signals for flow control. This connection is provided primarily for console access, but could be reconfigured for other purposes if needed.

A standard straight-through serial cable connected to a PC is required to access this console port. This port has the benefit of providing access to U-Boot and to early Linux boot log message, as opposed to the console access provided over the USB port, which provides neither. Use appropriate serial communications software such as minicom for Linux, or putty for Windows. Configure the port for 115200,8,N,1 (8 data bits, no handshake, 1 stop bit).

Figure 5-1 shows the pin numbering for the DB9 connector, while Table 5-1 gives a detailed description of the signals at X8.

Figure 5-1. RS-232 Connector X8 Pin Numbering

Table 5- 1. Connector X8 Pin Descriptions

| Pin | Signal          | I/O | Description    |

|-----|-----------------|-----|----------------|

| 1   | N/C             | -   | Not connected  |

| 2   | UART0_TXD_RS232 | 0   | UART0 transmit |

| 3   | UART0_RXD_RS232 | Ι   | UART0 receive  |

| 4   | N/C             | -   | Not connected  |

| 5   | GND             | -   | GND            |

| 6   | N/C             | -   | Not connected  |

| 7   | N/C             | -   | Not connected  |

| 8   | N/C             | -   | Not connected  |

| 9   | N/C             | -   | Not connected  |

## 6 USB Connectivity

## 6.1 USB Host (X3)

The USB1 interface signals route to the bottom connector of X3 (USB Dual Standard A and Ethernet). Note that the top USB connector of X3 is a not used. Although the USB interface of the Cosmic processor complies with USB 2.0 HS specification and supports dual role device configuration, due to its USB-A style connector, USB1 is limited to Host operation only.

The USB1 interface on the Cosmic board is equipped with ESD protection. It has its own 5V supply that is current limited by U4 (TPS2051B). It supports connection of different USB devices such as mass storage device, keyboard, and mouse.

To use the USB Host interface the board must be configured to provide power from the wall adapter input at X2 (see Figure 1-1). Set jumper JP1 to 1+2 to configure the board for wall power.

#### 6.2 USB OTG (X6)

The USB0 interface signals route to connector X6 (USB Micro-AB). The USB interface of the Cosmic processor complies with USB 2.0 HS specification. Firmware interaction configures the interface to act in host or Device mode, making it a dual role device but not a true OTG controller as described in more detail in the Cosmic processor Reference Manual.

The USB0 interface on the Cosmic board is equipped with ESD protection. USB0\_VBUS is connected to VBUS of the cable meaning USB0 is powered by the host.

This interface can be used both to power the board, and to provide serial console access. Connect a USB Standard-A to Micro-B, or Micro-AB cable between a host PC and connector X6. To configure the board for USB power, set jumper JP1 to 2+3 (see Figure 1-1). Once booted, the Cosmic Board shows up as a virtual serial port over USB. Use appropriate serial communications software such as minicom for Linux, or putty for Windows. Configure the port for 115200,8,N,1 (8 data bits, no handshake, 1 stop bit).

## 7 SD Card (X18)

The Cosmic board provides a Micro SD card slot at X18 for connection to the Cosmic's MMC0 interface. The interface is powered by an instant-on 3.3 V power supply and has card detect support (CDET) via the Cosmic processor A13 signal.

In addition to mass storage usage, the processor can boot from this interface. As the default boot mode of the phyCORE-Cosmic SOM, SD boot is selected by closing 3+4 pins of JP5 (see Figure 1-1).

#### 7.1 Inserting and Removing an SD Card

Insert a micro SD Card into slot X18, label down and pins facing up. After aligning the card with the connector, push to insert. The card will make a clicking sound and latch into the connector. To eject the card, push the card in to release. The connector will click and the card will be safe to remove. To avoid damaging the connector do not attempt to pull the card directly out without first pushing inward to release the lock mechanism.

## 8 HDMI (X16)

A High-Definition Multimedia Interface (HDMI) transmitter is connected to the parallel display interface of the processor. The interface is compliant with HDMI 1.4a specification and available through the micro HDMI connector at X16. Connection to an HDMI display is limited to 1920x1080 (1080p) @ 24 Hz due to Cosmic processor limitations and compatible display clock frequency limitations.

The 24-bit Cosmic LCD interface (3 x 8-bit RGB) along with the Multichannel audio serial port(McASP) signals are converted to HDMI signals by the HDMI transmitter at U1. The transmitter is configured by the processor via I2C and although operating at 1.8V, can handle the 3.3V processor signals. Along with delivering Consumer Electronic Control (CEC) the device also supports a low power or standby mode when HDMI is not being used. A port protection and interface device at U13 provides ESD protection, integrated level shifting of HDMI signals, and a 50 mA / 5V current-limited supply to the HDMI sink device (monitor, TV, projector, etc).

For access to the HDMI output, a micro HDMI cable is required. For connection to general HDMI compliant devices, an HDMI to Micro HDMI cable will typical be used.

The display signals that are connected to the HDMI interface (LCD\_D0 to LCD\_D15) are available at the expansion connector so that they can be used for other purposes such as connecting to an LCD expansion board. Refer to Chapter 13 for additional information.

Note: HDMI Connector not mounted on Revision 1.0 board.

#### 9 User Buttons

The Cosmic board is populated with four user accessible push buttons located at S1, S2, S3, and S4 to enable user input (see <u>Figure 1-1</u>). Each button is connected to a GPIO on the Cosmic processor. A detailed list of the user buttons is presented below.

- **S1** User Button 1 (BTN1). Pressing this button generates a debounced, active high signal to the processor at X\_GPIO1\_9. Holding this button will keep the output to held X\_GPIO1\_9 high. Releasing this button will keep the output to X\_GPIO1\_9 held low.

- **S2** User Button 2 (BTN2). Pressing this button generates a debounced, active high signal to the processor at X\_GPIO3\_4. Holding this button will keep the output to X\_GPIO3\_4 held high. Releasing this button will keep the output to X\_GPIO3\_4 held low.

- **S3** User Button 3 (BTN3). Pressing this button generates a debounced, active high signal to the processor at X\_GPIO1\_24. Holding this button will keep the output to X\_GPIO1\_24 held high. Releasing this button will keep the output to X\_GPIO1\_24 held low.

- **S4** User Button 4 (BTN4). Pressing this button generates a debounced, active high signal to the processor at X\_GPIO1\_20. Holding this button will keep the output to X\_GPIO1\_20 held high. Releasing this button will keep the output to X\_GPIO1\_20 held low.

## 10 System Reset Button (S5)

The Cosmic Board is equipped with a system reset button at S5. Pressing the button will toggle the X\_PB\_RESETn signal low and generate a manual system reset driving RESETn on the phyCORE-AM335x low.

The system reset signal, RESETn, is available on the Expansion connector (see Chapter 13 for more information) and can be used to reset various other peripheral devices. Refer to the PCM-051/phyCORE-AM335x Hardware Manual for details on the RESETn signal.

#### CAUTION:

When running Linux a proper system shutdown should be performed, or reboot executed instead of pressing the reset button. Pressing the reset button (or cutting power) without properly shutting down can cause file system errors and is not advised. Issue a poweroff or reboot command at the Linux prompt to avoid file system damage. Only use the reset button when not running Linux, or if the system freezes up.

#### 11 User LEDs

The Cosmic board is populated with four user programmable LEDs located at D11, D10, D4, and D5 to provide visual feedback to the user (see Figure 1-1). Each LED is connected to a GPIO on the Cosmic processor. A detailed list of the user LEDs is presented below.

- **D11** LED1 (Green). Connected to processor signal X\_GPIO3\_7. Drive signal X\_GPIO3\_7 high to turn this LED on and low to turn this LED off.

- **D10** LED2 (Green). Connected to processor signal X\_GPIO1\_27. Drive signal X\_GPIO1\_27 high to turn this LED on and low to turn this LED off.

- **D4** LED3 (Red). Connected to processor signal X\_GPIO1\_26. Drive signal X\_GPIO1\_26 high to turn this LED on and low to turn this LED off.

- **D5** LED4 (Red). Connected to processor signal X\_GPIO1\_21. Drive signal X\_GPIO1\_21 high to turn this LED on and low to turn this LED off.

## 12 Boot Selection (JP5)

Jumper JP5 provides a way to override the default boot option configured on the Cosmic SOM.

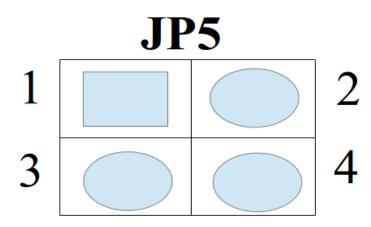

Figure 12-1. Jumper Numbering Scheme

Figure 12-1 shows the jumper pin numbering scheme. Pin 1 on the board is marked with a number one on the PCB silk screen. It is also visibly marked with a clipped corner on the component outline.

Table 12-1 shows the required jumper positions for configuring the desired boot device. Use jumper wires to connect the pins of JP5 based on the settings described.

By default JP5 is open, configuring the Cosmic for NAND boot.

| Table 12- 1. Jumper | Settings and | Descriptions |

|---------------------|--------------|--------------|

|---------------------|--------------|--------------|

| Jumper | Setting | Boot Device |

|--------|---------|-------------|

| JP5    | OPEN    | NAND        |

|        | 1+2,3+4 | NOR         |

|        | 3+4     | MMCO        |

## 13 Real-Time Clock Options (RTC)

There are two options for an RTC on the Cosmic-AM335x.

## 13.1 PMIC RTC

The Power Management IC at U4 includes an integrated RTC. This RTC includes alarm and time keeping functions. The RTC is supplied by the main system power when it is on, and by the backup battery voltage VBAT\_IN\_4RTC, if present, when the main system power is off and the jumper J10 has been moved from its default position of (1+2) to position (2+3).

#### 13.2 AM335x RTC

The AM335x processor also includes an integrated RTC. However, the RTC integrated in the AM335x uses significantly more power than the RTC in the PMIC. Because of this power disadvantage, the SOM has not been designed to support the AM335x RTC with backup power.

To backup the RTC on the module, a secondary voltage source of 3 V can be attached to the Cosmic-AM335x at Jumper **JP4**. This voltage source supplies the backup voltage domain VBAT of the AM335x which supplies the RTC and some critical registers when the primary system power, VDD\_3V3, is removed.

## 14 Controller Area Network (CAN) Interfaces

The Controller Area Network (CAN) is a serial communications protocol which efficiently supports distributed real time control with a high level of security.

The CAN interface is accessible at the connector X25.

The PHYTEC cosmic board provides access to the CAN0 signals which are multiplexed onto the AM335x UART1\_TX and UART1\_RX pins. These signals route from the phyCORE connector to a CAN transceiver. The signals out of the transceiver route to X25.

Jumper JP3 can be installed to add a 120 Ohm termination resistor across the CAN data lines if needed.

| Pin | Signal | I/O | Description   |

|-----|--------|-----|---------------|

| 1   | N/C    | -   | Not connected |

| 2   | GND    | -   | GND           |

| 3   | CAN _L | Ю   | Can Low       |

| 4   | CAN_H  | IO  | Can High      |

| 5   | GND    | -   | GND           |

| 6   | N/C    | -   | Not connected |

| 7   | N/C    | -   | Not connected |

| 8   | N/C    | -   | Not connected |

| 9   | N/C    | -   | Not connected |

| 10  | N/C    | -   | Not connected |

Table 14- 1. Connector X25 Pin Descriptions

## 15 Expansion Connectors (X19, X20)

Two 2x30 2mm Expansion connectors (X19 and X20) provide easy access to many of the phyCORE-AM335x signals. All processor signals on the Expansion connector are 3.3 V. As an accessory, add-on expansion boards such as LCD and WiFi are made available through PHYTEC to connect to the Expansion connectors.

Most of the signals routed to the expansion connector have been configured for a given pin muxed function. Using these signals are alternate functions requires BSP modifications.

Tables detailing signal mapping of the Expansion Connectors are provided below. These tables list only the primary function intended on the Cosmic Board, but can be reconfigured for many other purposes. Refer to the AM335x Technical Reference manual on available operation modes.

| Signal      | Expansion Connector Pin                                        | Description                                           |

|-------------|----------------------------------------------------------------|-------------------------------------------------------|

| VCC_5V0     | X19-1, X19-3                                                   | 5V power from currently selected source (wall or USB) |

| VCC_3V3     | X19-2, X19-4                                                   | 3.3V voltage domain                                   |

| 5V_IN       | X19-5                                                          | 5V power from wall adapter input                      |

| X_USB0_VBUS | X19-8                                                          | 5V power from USB OTG connector                       |

| GND         | X19-7, X19-10, X19-59, X19-60,<br>X20-1, X20-2, X20-59, X20-60 | Ground                                                |

Table 15- 2. Power Signal Map

## Table 15- 3. System Signal Map

| Signal      | Expansion Board Pin | Туре | Description                                                 |

|-------------|---------------------|------|-------------------------------------------------------------|

| X_PB_RESETn | X20-58              | 0    | System reset signal; can be used to reset external devices. |

| X_CLKOUT1   | X19-12              | 0    | CKLOUT1; free for external use                              |

## Table 15- 4. JTAG Signal Map

| Signal  | Expansion Board Pin | Туре | Description           |

|---------|---------------------|------|-----------------------|

| X_TDO   | X19-18              | 0    | JTAG test data output |

| X_TMS   | X19-20              | 0    | JTAG test mode select |

| X_TCK   | X19-14              | 0    | JTAG test clock input |

| X_nTRST | X19-22              |      | JTAG test reset       |

| X_TDI | X19-16 | I | JTAG test data input |

|-------|--------|---|----------------------|

## Table 15- 5. CAN Signal Map

| Signal    | Expansion Board Pin | Туре | Description                                   |

|-----------|---------------------|------|-----------------------------------------------|

| X_GPIO1_9 | X19-50              | I    | CAN1_RX; connected to PCL-051 CAN transceiver |

| X_GPIO1_8 | X19-44              | 0    | CAN1_TX; connected to PCL-051 CAN transceiver |

## Table 15- 6. I2C Signal Map

| Signal                       | Expansion Board Pin | Туре | Description                                                     |

|------------------------------|---------------------|------|-----------------------------------------------------------------|

| X_UART1_RXD/_<br>P_UART0_RXD | X19-35              | I/O  | I2C1_SDA clock (open drain with pull-up resistor on the SOM)    |

| X_UART1_TXD/_<br>P_UART0_TXD | X19-37              | I/O  | I2C1_SCL data (open drain with pull-<br>up resistor on the SOM) |

| X_UART1_RTS                  | X19-39              | I/O  | I2C2_SCL data (open drain with pull-<br>up resistor on the SOM) |

| X_UART1_CTS                  | X19-41              | I/O  | I2C2_SDA data (open drain with pull-<br>up resistor on the SOM) |

## Table 15-7. UART Signal Map

| Signal                       | Expansion Board Pin | Туре | Description            |

|------------------------------|---------------------|------|------------------------|

| X_UART1_TXD/_P_UART0_TX<br>D | X19-37              | 0    | UART 1 transmit data   |

| X_UART1_RXD/_P_UART0_RX<br>D | X19-35              | I    | UART 1 recieve data    |

| X_UART1_RTS                  | X19-39              | 0    | UART 1 request to send |

| X_UART1_CTS                  | X19-41              | I    | UART 1 clear to send   |

| X_UART2_RX                   | X19-47              | I    | UART 2 recieve data    |

| X_UART2_TX                   | X19-49              | 0    | UART 2 transmit data   |

| X_UART3_RX                   | X19-43              | I    | UART 3 recieve data    |

| X_UART3_TX                   | X19-45              | 0    | UART 3 transmit data   |

| X_GPIO1_8                    | X19-44              | I    | UART 4 recieve data    |

| X_GPIO1_9                    | X19-50              | 0    | UART 4 transmit data   |

© PHYTEC Embedded Pvt. Ltd 2013

| X_MII1_RCTL/_GPIO3_4    | X19-51 | 0 | UART 5 transmit data |

|-------------------------|--------|---|----------------------|

| X_MII1_COL/_MCASP1_AXR2 | X19-57 | I | UART 5 recieve data  |

# Table 15- 8. SPI Signal Map

| Signal                      | Expansion Board Pin | Туре | Description               |

|-----------------------------|---------------------|------|---------------------------|

| X_SPI0_SCLK                 | X19-46              | 0    | SPI0 clock                |

| X_SPI0_CS0                  | X19-48              | 0    | SPI0 chip select 0        |

| X_SPI0_D1                   | X19-56              | I/O  | SPI0 Data1 input / output |

| X_SPI0_D0                   | X19-58              | I/O  | SPI0 Data0 input / output |

| X_GPIO3_17                  | X19-40              | 0    | SPI1 chip select 0        |

| X_MII1_COL/_MCASP1_A<br>XR2 | X19-57              | 0    | SPI1 clock                |

| X_MCASP0_AXR0               | X20-49              | I/O  | SPI1 Data1 input / output |

| X_MCASP0_FSX                | X20-53              | I/O  | SPI1 Data0 input / output |

| X_ECAP0_IN_PWM0_OU<br>T     | X20-55              | 0    | SPI1 chip select 1        |

Table 15- 9. ADC Signal Map

| Signal | Expansion Board Pin | Туре   | Description                       |

|--------|---------------------|--------|-----------------------------------|

| X_AIN0 | X19-24              | Analog | ADC input0; free for external use |

| X_AIN1 | X19-26              | Analog | ADC input1; free for external use |

| X_AIN2 | X19-28              | Analog | ADC input2; free for external use |

| X_AIN3 | X19-30              | Analog | ADC input3; free for external use |

| X_AIN4 | X19-32              | Analog | ADC input4; free for external use |

| X_AIN5 | X19-34              | Analog | ADC input5; free for external use |

| X_AIN6 | X19-36              | Analog | ADC input6; free for external use |

| X_AIN7 | X19-38              | Analog | ADC input7; free for external use |

| Signal                      | Expansion Board Pin | Туре | Description                                                                            |

|-----------------------------|---------------------|------|----------------------------------------------------------------------------------------|

| X_GPMC_AD0                  | X20-33              | I/O  | General Purpose Memory Controller interface Address/Data                               |

| X_GPMC_AD1                  | X20-35              | I/O  | General Purpose Memory Controller interface Address/Data                               |

| X_GPMC_AD2                  | X20-37              | I/O  | General Purpose Memory Controller interface Address/Data                               |

| X_GPMC_AD3                  | X20-39              | I/O  | General Purpose Memory Controller interface Address/Data                               |

| X_GPMC_AD4                  | X20-41              | I/O  | General Purpose Memory Controller interface Address/Data                               |

| X_GPMC_AD5                  | X20-43              | I/O  | General Purpose Memory Controller interface Address/Data                               |

| X_GPMC_AD6                  | X20-32              | I/O  | General Purpose Memory Controller interface Address/Data                               |

| X_GPMC_AD7                  | X20-34              | I/O  | General Purpose Memory Controller interface Address/Data                               |

| X_GPMC_ADVn_A<br>LE         | X20-36              | 0    | General Purpose Memory Controller<br>interface address valid / address latch<br>enable |

| X_GPMC_BE0n_C<br>LE         | X20-38              | 0    | General Purpose Memory Controller<br>interface byte enable 0 / command<br>latch enable |

| X_GPMC_OEn_R<br>En          | X20-42              | 0    | General Purpose Memory Controller output enable / read enable                          |

| X_GPMC_WAIT/_<br>P_MII1_COL | X20-44              | I/O  | General Purpose Memory Controller<br>WAIT / PRU Ethernet0 collision                    |

| X_GPMC_WEn                  | X20-46              | 0    | General Purpose Memory Controller write enable                                         |

# Table 15- 11. LCD Signal Map

| Signal   | Expansion Board Pin | Туре | Description    |

|----------|---------------------|------|----------------|

| X_LCD_D0 | X20-19              | 0    | LCD data bit 0 |

| X_LCD_D1 | X20-21              | 0    | LCD data bit 1 |

| X_LCD_D2 | X20-23              | 0    | LCD data bit 2 |

| X_LCD_D3 | X20-25              | 0    | LCD data bit 3 |

| X_LCD_D4 | X20-27              | 0    | LCD data bit 4 |

|                         |        | 1 |                                                              |  |

|-------------------------|--------|---|--------------------------------------------------------------|--|

| X_LCD_D5                | X20-4  | 0 | LCD data bit 5                                               |  |

| X_LCD_D6                | X20-6  | 0 | LCD data bit 6                                               |  |

| X_LCD_D7                | X20-8  | 0 | LCD data bit 7                                               |  |

| X_LCD_D8                | X20-10 | 0 | LCD data bit 8                                               |  |

| X_LCD_D9                | X20-12 | 0 | LCD data bit 9                                               |  |

| X_LCD_D10               | X20-14 | 0 | LCD data bit 10                                              |  |

| X_LCD_D11               | X20-22 | 0 | LCD data bit 11                                              |  |

| X_LCD_D12               | X20-24 | 0 | LCD data bit 12                                              |  |

| X_LCD_D13               | X20-26 | 0 | LCD data bit 13                                              |  |

| X_LCD_D14               | X20-28 | 0 | LCD data bit 14                                              |  |

| X_LCD_D15               | X20-30 | 0 | LCD data bit 15                                              |  |

| X_LCD_D16               | X20-17 | 0 | LCD data bit 16                                              |  |

| X_LCD_D17               | X20-20 | 0 | LCD data bit 17                                              |  |

| X_LCD_D18               | X20-15 | 0 | LCD data bit 18                                              |  |

| X_LCD_D19               | X20-31 | 0 | LCD data bit 19                                              |  |

| X_LCD_D20               | X20-18 | 0 | LCD data bit 20                                              |  |

| X_LCD_D21               | X20-13 | 0 | LCD data bit 21                                              |  |

| X_LCD_D22               | X20-29 | 0 | LCD data bit 22                                              |  |

| X_LCD_D23               | X20-16 | 0 | LCD data bit 23                                              |  |

| X_LCD_PCLK              | X20-7  | 0 | LCD Pixel Clock                                              |  |

| X_LCD_AC_BIAS_EN        | X20-11 | 0 | LCD Bias enable chip select                                  |  |

| X_ECAP0_IN_PWM0_OU<br>T | X20-55 | 0 | PWM output, can be used<br>for display brightness<br>control |  |

| X_LCD_VSYNC             | X20-5  | 0 | LCD Vertical synchronization                                 |  |

| X_LCD_HSYNC             | X20-3  | 0 | LCD Horizontal synchronization                               |  |

# Table 15- 12. Multichannel Audio Serial Ports (McASP) Signal Map

| Signal        | Expansion Board Pin | Туре | Description                    |

|---------------|---------------------|------|--------------------------------|

| X_McASP0_AXR0 | X20-49              | I/O  | serial data                    |

| X_McASP0_FSX  | X20-53              | I/O  | frame synchronization transmit |

| X_McASP0_AHCLKX | X20-47 | I/O | high frequency clock |

|-----------------|--------|-----|----------------------|

| X_McASP0_AXR1   | X20-51 | I/O | serial data          |

| X_McASP0_ACLKX  | X20-45 | I/O | transmit bit clock   |

# Table 15- 13. General Purpose I/O's (GPIO's) Signal Map